# On the co-design of electronics and photonics for optical communication

### Bahaa Radi

# Department of Electrical & Computer Engineering McGill University Montréal, Québec, Canada

June 23, 2020

A thesis submitted to McGill University in partial fulfillment of the requirements of the degree of

Doctor of Philosophy

©2020 Bahaa Radi

## Abstract

The explosive growth of internet traffic has led to an increase in data communication within data centers that use optical interconnects for communication. This calls for the development of low-power, high-speed, and high-sensitivity optical receivers to support this increased communication. Additionally, with silicon photonic technologies offering new design opportunities, the co-design of electronics and photonics could lead to more efficient, improved receivers. Under the umbrella of electronics/photonics co-design, this thesis explores two themes: 1) the design of energy-efficient optical receivers that leverage silicon photonics to replace clock phase generation circuits and, 2) the implementation of passives, that are conventionally found on the electronic side, in the silicon photonic technology stack.

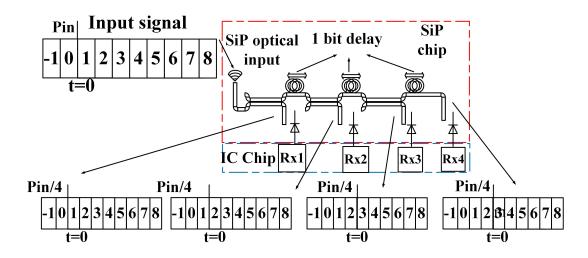

Under the first theme, three optical receivers are designed. The first receiver is a conventional front-end 12.5 Gb/s optical receiver that uses a silicon photonic structure to split the input signal into four data streams and delay each stream by one bit relative to the next. In this fashion, demultiplex-by-four outputs, that are conventionally obtained by

Abstract

using four quadrature phases, can be obtained with only a single clock phase. technique reduces the power consumption of clock phase generation from 30-45 % as reported in the literature to around 10 % of the total power consumption of the receiver. This receiver has an energy efficiency of 1.93 pJ/bit and a sensitivity of -4 dBm excluding optical splitting losses. The second receiver improves upon the first receiver by using a high-bandwidth gain-improved transimpedance amplifier with a pseudo-differential-output followed by a comparator. This receiver also reduces the number of data streams from four to two, decreasing the optical losses at the input and simplifying the receiver. This receiver achieves a speed of 17 Gb/s, a sensitivity of -7 dBm including 3 dB optical losses, and an energy efficiency of 156 fJ/bit, the best reported energy-efficiency at the time of writing this thesis. Finally, to improve the speed, a third receiver with a novel two-bit integrating front was developed. The low-bandwidth front-end of this receiver allows the receiver to operate at higher data rates for a given bandwidth and addresses the issue of having conventional power-hungry transimpedance amplifiers at the input that do not scale well with the technology node. This receiver achieves a speed of 22 Gb/s. All three receivers are fabricated and validated experimentally.

The second theme explores three passive structures implemented in the silicon photonics stack. The first is a 15 GHz on-chip monopole antenna. The antenna is designed, fabricated, and RF inter-chip data transmission in silicon photonics is demonstrated for the first time. The second structure explores the design of a low-pass filter driven by a

Abstract

photodetector. Design methodology, fabrication, and measurements are presented and compared to simulation values. Finally, a moving average filter is developed using optical delay lines, photodetectors, and a capacitor. Experimental validation confirms proper 1-bit moving average operation at 2.5 Gb/s, and 2-bits moving average operation at 5 Gb/s.

## Abrégé

La croissance explosive du trafic Internet a entraîné une augmentation de la communication de données au sein des centres de données qui utilisent des interconnexions optiques pour la communication. Cela nécessite le développement de récepteurs optiques à basse consommation, haute vitesse et haute sensibilité pour soutenir cette communication accrue. De plus, avec les nouvelles opportunités d'innovation offertes par les technologies photoniques en silicium, la co-conception de l'électronique et de la photonique pourrait mener à des récepteurs plus efficaces et améliorés. Sous l'égide de la co-conception électronique / photonique, cette thèse explore deux thèmes: 1) la conception de récepteurs optiques écoénergétiques qui exploitent la photonique au silicium pour remplacer les circuits de génération de phase d'horloge et, 2) la mise en œuvre d'éléments passifs, qui sont conventionnellement trouvés du côté électronique, dans la technologie photonique en silicium.

À propos du premier thème, trois récepteurs optiques sont conçus. Le premier récepteur est un récepteur optique frontal classique de 12.5 Gb/s qui utilise une structure photonique

Abrégé v

en silicium pour diviser le signal d'entrée en quatre flux de données et retarder chaque flux d'un bit par rapport au suivant. De cette manière, les sorties démultiplexées par quatre, qui sont généralement obtenues en utilisant quatre phases en quadrature, peuvent être obtenues avec une seule phase d'horloge. Cette technique réduit la consommation d'énergie dans la génération de la phase d'horloge de 30 à 45 % comme indiqué dans la littérature à environ 10 % de la consommation d'énergie totale du récepteur. Ce récepteur a une efficacité énergétique de 1.93 pJ/bit et une sensibilité de -4 dBm excluant les pertes de division optique. Le deuxième récepteur améliore le premier récepteur en utilisant un amplificateur à transimpédance à bande passante élevée et à gain amélioré avec une sortie pseudo-différentielle suivie d'un comparateur. Ce récepteur réduit également le nombre de flux de données de quatre à deux, ce qui diminue les pertes optiques à l'entrée et simplifie le récepteur. Ce récepteur est capable d'atteindre une vitesse de 17 Gb/s, une sensibilité de -7 dBm incluant des pertes optiques de 3 dB, et une efficacité énergétique de 156 fJ/bit, ce qui est la meilleure efficacité énergétique rapportée au moment de la rédaction de cette thèse. Enfin, pour améliorer la vitesse, un troisième récepteur avec un nouveau front d'intégration à deux bits a été développé. Ce récepteur frontal à faible bande passante permet au récepteur de fonctionner à des débits de données plus élevés pour une bande passante donnée et résout le problème d'avoir à l'entrée des amplificateurs de transimpédance énergivores qui ne s'adaptent pas bien avec le nœud technologique. Ce récepteur atteint une vitesse de 22 Gb/s. Les trois récepteurs sont fabriqués et validés expérimentalement.

Abrégé vi

Le deuxième thème examine trois structures passives implémentées dans la technologie photonique en silicium. Le premier est une antenne monopôle sur puce de 15 GHz. L'antenne est conçue, fabriquée et la transmission de données RF entre puces en photonique sur silicium est démontrée pour la première fois. La deuxième structure explore la conception d'un filtre passe-bande connecté à un photodétecteur. La méthodologie de conception, la fabrication et les mesures sont présentées et comparées aux valeurs de simulation. Enfin, un filtre à moyenne mobile est développé à l'aide de lignes à retard optiques, de photodétecteurs et d'un condensateur. La validation expérimentale confirme le fonctionnement de la moyenne mobile à 1 bit à 2.5 Gb/s et le fonctionnement à moyenne mobile de 2 bits à 5 Gb/s.

## Acknowledgements

I would like to thank my advisor, Prof. Odile Liboiron-Ladouceur for this fascinating journey. This research would not have been possible without her guidance, discussions, and encouragement. She also helped me to improve my presentation skills and writing skills. I am truly grateful for her advice. She also though me to take some opportunities that may not look attractive at first, but then proved to be very valuable. I learned more than just research skills from her.

I would like to also acknowledge Prof. Frédéric Nabki and Prof. Michaël Ménard with their close involvement with the majority of my research. The provided constant feedback and took the time to meet very frequently with me to support this research and thesis. I thank them very much for their help and support. This research would not be the same without their help.

I would like to thank Prof. Gordon Roberts for being in my PhD committee and providing some interesting general feedback on the work I was doing. I learned a lot from his insight.

I would like to thank Prof. Tony Chan Carusone for agreeing to take the time to read

my thesis and to be the external examiner. I would also like to thank Prof. Ke Wu and Prof. Boris Vaisband for taking the time to be on the defense committee.

I would like to specifically thank Mohammadreza Sanadgol Nezami, Mohammad Taherzadeh-Sani, Ajaypal Singh Dhillon, Vernon Elmo-Paul, and Yule Xiong for their help with my research and for being excellent collaborators.

I acknowledge the financial support I received from McGill university through thes McGill Engineering Doctoral Awards (MEDA). I would not have been able to pursue a PhD without this. I also acknowledge the contribution of the Canadian Microelectronics Corporation (CMC) for giving me access to their design tools and for subsidizing the fabrication of my chips. I also acknowledge the professors of The Photonic Systems Group who allowed me to use the equipment needed to measure my chips.

I would like to thank some of my close friends, Ahmad Saleh, Kahlil Hindawi, Feras Elsaid, and Yazan Alem who shared my struggles of doing a PhD and certainly made it more bearable.

I would like to thank my fiancée Rwan Salah for being very supportive. I am very lucky to have met you in my final year while you made my life much more exciting. You are the flower of my life.

Finally, my deepest appreciation goes to my parents, Sanaa Ghneam and Ishaq Radi, who offered the utmost genuine and honest unconditional support that a human being could ever receive. I would not be where I am today without them. I dedicate this work to them.

# Contents

| 1 | Intr | roduction |                                                          |    |

|---|------|-----------|----------------------------------------------------------|----|

|   | 1.1  | Motiv     | ation                                                    | 2  |

|   | 1.2  | Thesis    | s objectives                                             | 3  |

|   | 1.3  | Claim     | of Originality                                           | 6  |

|   |      | 1.3.1     | Publications and contributions of the author             | 8  |

|   | 1.4  | Thesis    | s Organization                                           | 14 |

| 2 | Bac  | kgrou     | nd                                                       | 16 |

|   | 2.1  | An ov     | erview of silicon photonics                              | 16 |

|   |      | 2.1.1     | Motivation for passives electronics in Silicon Photonics | 21 |

|   |      | 2.1.2     | A note on process variations in Silicon Photonics        | 23 |

|   | 2.2  | Motiv     | ation for optical versus electronic delay lines          | 24 |

|   |      | 2.2.1     | CMOS Delay Lines                                         | 25 |

|   |      | 222       | Optical delay lines                                      | 29 |

Contents x

|   |            | 2.2.3 T    | Trade-off considerations                                                  | 32 |

|---|------------|------------|---------------------------------------------------------------------------|----|

|   | 2.3        | Optical r  | receivers with demultiplexed output                                       | 34 |

|   |            | 2.3.1 B    | Brief overview of conventional source-synchronous optical receivers       | 34 |

|   |            | 2.3.2 C    | Clock phases in optical receivers                                         | 35 |

|   |            | 2.3.3 F    | ront-end bandwidth                                                        | 37 |

|   | 2.4        | Optical s  | split and delay structure                                                 | 38 |

|   | 2.5        | Summar     | y                                                                         | 40 |

| 3 | An         | Optical I  | Receiver Exploiting SiP Delays for Clock Phases Replacement               | 41 |

|   | 3.1        | Introduc   | tion                                                                      | 41 |

|   | 3.2        | System A   | Architecture                                                              | 43 |

|   | 3.3        | PCB par    | rasitics and AC coupling noise analysis                                   | 47 |

|   | 3.4        | Experim    | ental validation                                                          | 52 |

|   | 3.5        | Discussio  | on                                                                        | 58 |

|   | 3.6        | Conclusion | on                                                                        | 59 |

| 4 | <b>A</b> 1 | 7 Gbps 1   | 156 fJ/bit Two-Channel Optical Receiver in 65 nm CMOS                     | 61 |

|   | 4.1        | Two-chai   | nnel optical receivers overview                                           | 62 |

|   |            | 4.1.1 T    | Wo-phase clocked receiver                                                 | 62 |

|   |            | 4.1.2 T    | Two channel optical split and delay receiver                              | 63 |

|   | 4.2        | Design o   | of the two-channel electronic receiver with optical-input split and delay | 66 |

Contents xi

|   |     | 4.2.1        | Electronic receiver architecture                                       | 67  |

|---|-----|--------------|------------------------------------------------------------------------|-----|

|   |     | 4.2.2        | Transimpedance amplifier with single-ended-input and differential      |     |

|   |     |              | output                                                                 | 69  |

|   |     | 4.2.3        | High-speed comparator with offset nulling and latch                    | 74  |

|   | 4.3 | Measu        | rement results                                                         | 77  |

|   | 4.4 | Concl        | usion                                                                  | 83  |

| 5 | A 2 | $2~{ m Gb}/$ | s Time-Interleaved Optical Receiver with Integrating Front-end         | 85  |

|   | 5.1 | Introd       | luction                                                                | 86  |

|   | 5.2 | Low-b        | andwidth receiver architecture                                         | 88  |

|   |     | 5.2.1        | Integrating receiver front-end                                         | 88  |

|   |     | 5.2.2        | Resettable receiver, current-amplifier-based receivers, and integrate- |     |

|   |     |              | and-dump receiver                                                      | 92  |

|   | 5.3 | Propo        | sed time-interleaved receiver                                          | 97  |

|   |     | 5.3.1        | Architecture and operation                                             | 97  |

|   |     | 5.3.2        | Analysis of the integration                                            | 103 |

|   |     | 5.3.3        | Noise in the two-bit integrating front-end receiver and input          |     |

|   |     |              | capacitance impact on SNR                                              | 107 |

|   |     | 5.3.4        | Detailed circuit implementation                                        | 109 |

|   | 5.4 | Exper        | imental results                                                        | 115 |

|   | 5.5 | Discus       | ssion                                                                  | 121 |

Contents xii

|   | 5.6  | A note on the silicon-photonic structures compatible with the two-bit |     |

|---|------|-----------------------------------------------------------------------|-----|

|   |      | integrating front-end receiver                                        | 129 |

|   | 5.7  | Conclusion                                                            | 134 |

| 6 | Den  | nonstration of Inter-chip Transmission with On-Chip Antennas in SiP   | 135 |

|   | 6.1  | Introduction                                                          | 136 |

|   | 6.2  | Antenna design                                                        | 138 |

|   | 6.3  | Experimental validation                                               | 142 |

|   | 6.4  | Discussion                                                            | 146 |

|   | 6.5  | Conclusion                                                            | 148 |

| 7 | Inte | egrated RF Passive Low-Pass Filters in Silicon Photonics              | 149 |

|   | 7.1  | Introduction                                                          | 149 |

|   | 7.2  | Circuit model and design parameters                                   | 152 |

|   | 7.3  | Experimental results                                                  | 156 |

|   | 7.4  | Conclusion                                                            | 161 |

| 8 | A H  | High-speed Moving Average Integrator in SiP for TIA-less Receivers    | 162 |

|   | 8.1  | Introduction                                                          | 163 |

|   | 8.2  | Design methodology                                                    | 164 |

|   | 8.3  | Data recovery principle                                               | 168 |

|   | 8.4  | Experimental procedure and results                                    | 171 |

|   | 8.5 | Concl            | $\operatorname{usion}$                             | 173 |

|---|-----|------------------|----------------------------------------------------|-----|

| 9 | Pro | $\mathbf{posed}$ | Future Work and Conclusions                        | 176 |

|   | 9.1 | Propo            | sed future work                                    | 176 |

|   |     | 9.1.1            | Final integration of photonic and electronic chips | 177 |

|   |     | 9.1.2            | Monolithic design                                  | 177 |

|   |     | 9.1.3            | Clock recovery for the optical receivers           | 178 |

|   |     | 9.1.4            | A silicon photonics based delay locked loop        | 179 |

|   | 9.2 | Concl            | usions                                             | 179 |

# List of Figures

| 1.1 | Data traffic per year in data centers [1]                                  | 2  |

|-----|----------------------------------------------------------------------------|----|

| 1.2 | Data traffic breakdown by destination [1]                                  | 2  |

| 2.1 | Silicon photonics process cross-section [17]                               | 17 |

| 2.2 | Silicon photonics process cross-section [17]                               | 18 |

| 2.3 | Photodetector model in [19]                                                | 19 |

| 2.4 | Layout of an N-channel MOSFET next to two MIM capacitors illustrating      |    |

|     | that passives can much larger area compared to transistors                 | 22 |

| 2.5 | Summary of benefits of relocating passives from the IC side to the silicon |    |

|     | photonics side.                                                            | 24 |

| 2.6 | Inverter-based tapped delay line                                           | 26 |

| 2.7 | Single output delay line                                                   | 27 |

| 2.8 | Two path delay line capable of sub-gate delays                             | 27 |

List of Figures xv

| 2.9  | Analog buffer that can be used to delay analog signals and controlled through |    |

|------|-------------------------------------------------------------------------------|----|

|      | adjusting the load                                                            | 28 |

| 2.10 | Supply controlled delay line                                                  | 29 |

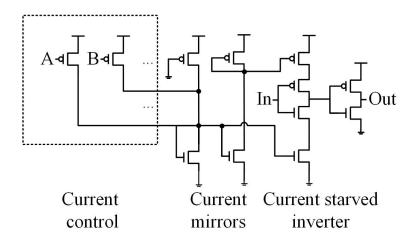

| 2.11 | Current starved delay line                                                    | 30 |

| 2.12 | Optical delay line model                                                      | 30 |

| 2.13 | Electronically tunable optical delay lines                                    | 32 |

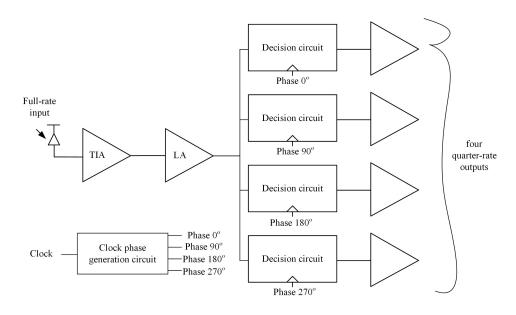

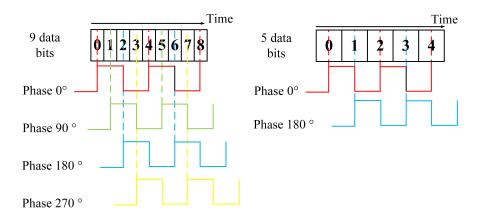

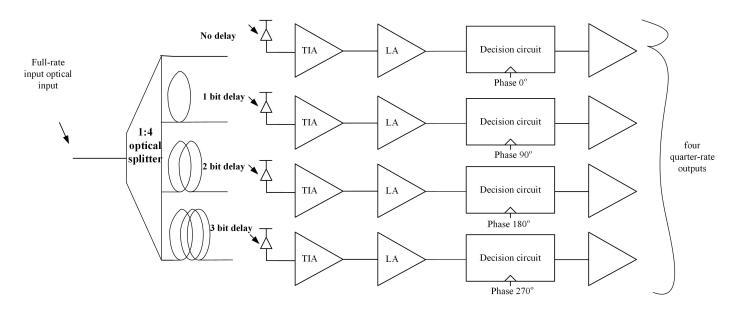

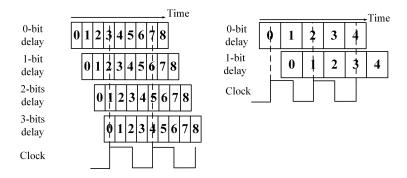

| 2.14 | Conventional optical receiver with demultiplexed outputs                      | 36 |

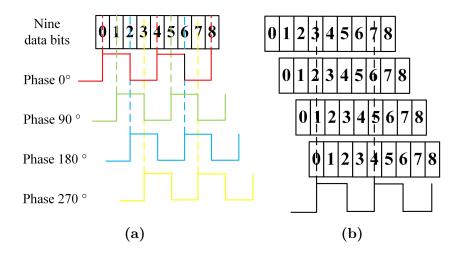

| 2.15 | Sampling in conventional four clock phase receiver (left) and two clock phase |    |

|      | receiver (right)                                                              | 36 |

| 2.16 | An optical receiver architecture that uses split and delay functionality to   |    |

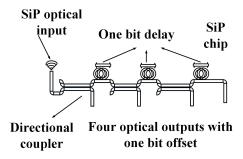

|      | produce demultiplexed outputs                                                 | 37 |

| 2.17 | Sampling in using silicon photonics structure with four quarter-rate outputs  |    |

|      | (left) and two half-rate outputs (right)                                      | 38 |

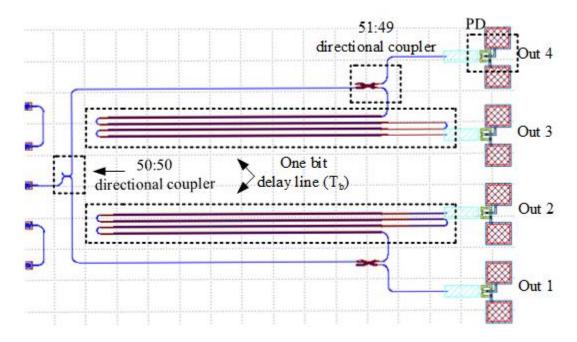

| 2.18 | Optical split-delay structure                                                 | 36 |

| 3.1  | (a) Sampling in conventional optoelectronic receiver with four clock phases.  |    |

|      | (b) Sampling in the proposed system using four different delays               | 43 |

| 3.2  | The SiP chip is outlined in red while the IC is outlined in blue              | 44 |

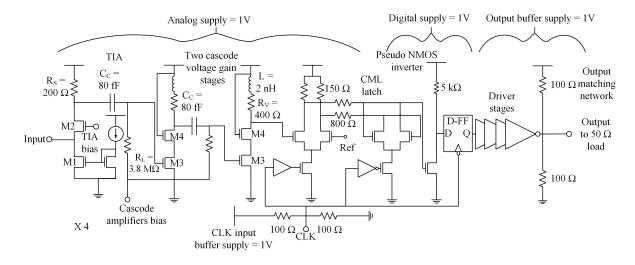

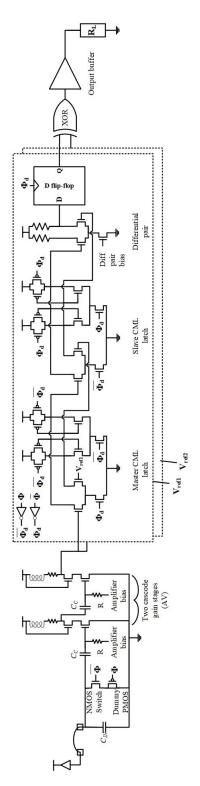

| 3.3  | Detailed circuit implementation of one of the four sub-receivers              | 46 |

| 3.4  | Sampling of amplified bits to generate quarter rate output                    | 47 |

| 3.5  | Ac simulations with idea photodetector                                        | 48 |

List of Figures xvi

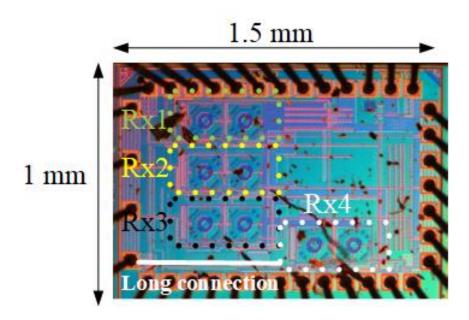

| 3.6  | A micrograph of the IC chip. The IC is wire bonded to a QFN-80 package                 |    |

|------|----------------------------------------------------------------------------------------|----|

|      | (not shown) mounted on a high-speed low-loss RO4350B PCB                               | 49 |

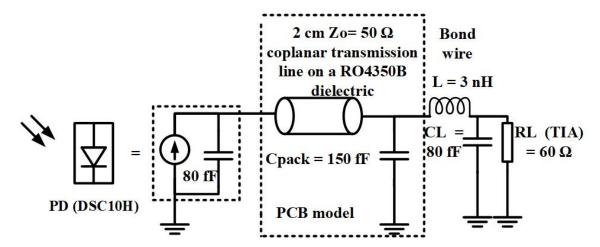

| 3.7  | Model of the PCB interconnect and package between the PD and the input                 |    |

|      | of each sub receiver                                                                   | 50 |

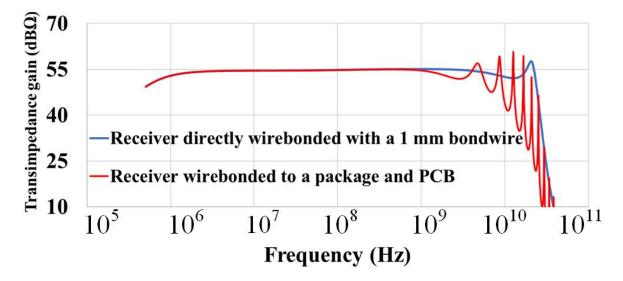

| 3.8  | AC simulations comparing the performance of the IC chip when wire bonded               |    |

|      | to a PD compared to the IC mounted on a PCB                                            | 51 |

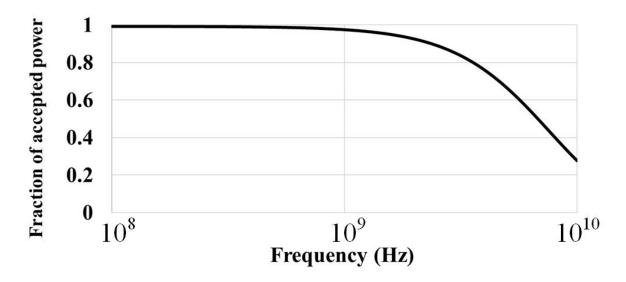

| 3.9  | The fraction of accepted power versus frequency due to parasitics at the input.        | 52 |

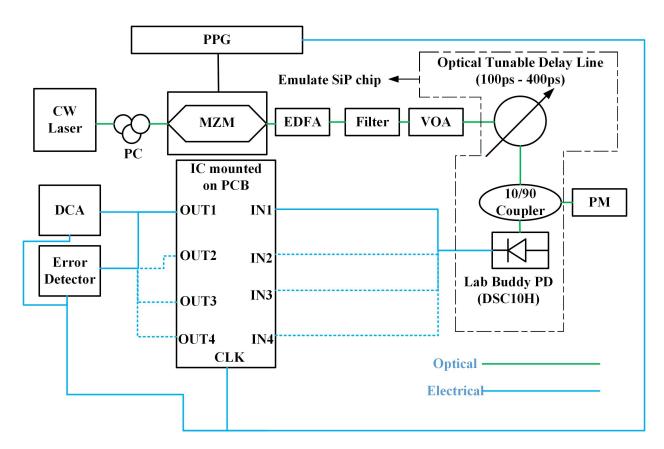

| 3.10 | Test setup for the IC in the receiver using an external photodetector module.          |    |

|      | The dashed outline represents the components used to emulate the SiP chip.             |    |

|      | Dotted lines represent the change of the connection between the PD and the             |    |

|      | input of the IC for testing of each of the four channels                               | 54 |

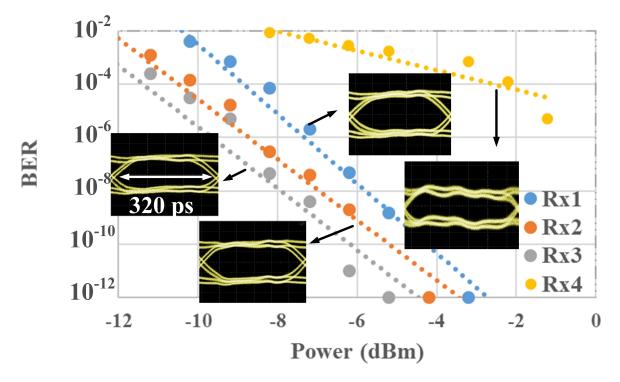

| 3.11 | The measured BER curve for each of the sub receivers with the four output              |    |

|      | eye diagrams with a data rate of $3.125~\mathrm{Gb/s}$ . Output eye diagrams are shown |    |

|      | for $10^{-12}$ for Rx1-Rx3 and approximately $10^{-6}$ for Rx4                         | 55 |

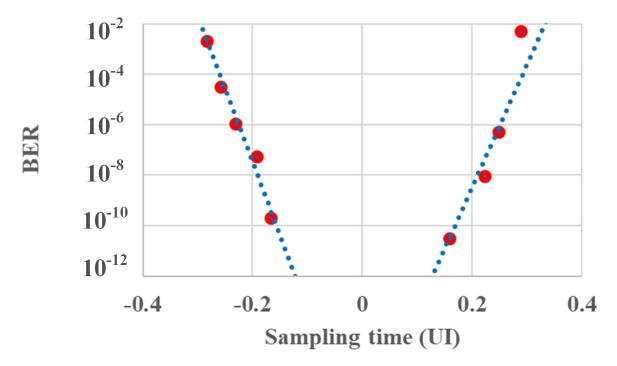

| 3.12 | Bathtub curve measurements of the receiver for a 12.5 Gb/s input                       | 56 |

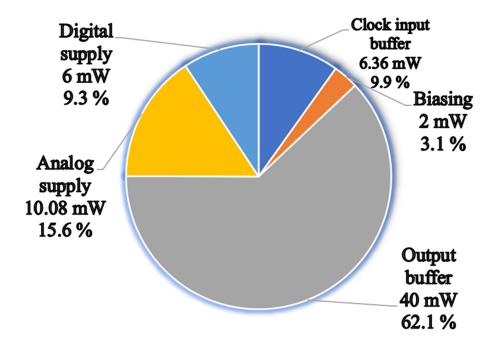

| 3.13 | Power consumption breakdown                                                            | 57 |

List of Figures xvii

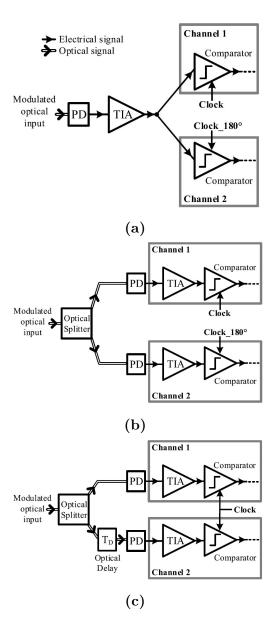

| 4.1  | (a) A conventional two-channel receiver architecture that splits the paths after          |    |

|------|-------------------------------------------------------------------------------------------|----|

|      | the TIA, and requires the Clock and $Clock\_180^o$ (i.e., the clock signal that           |    |

|      | is shifted by $180^{\circ}$ ) phases; (b) a two-channel receiver architecture that splits |    |

|      | the paths before the PD, and requires the Clock and $Clock_{-}180^{o}$ phases; (c)        |    |

|      | the proposed two-channel receiver architecture that splits the paths before the           |    |

|      | PD and only requires one clock phase for its comparators                                  | 64 |

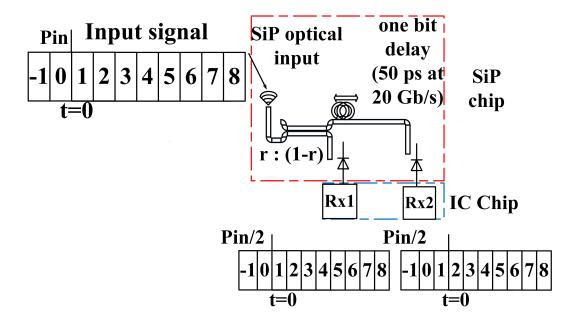

| 4.2  | Silicon photonics (SiP) split-delay structure schematic with envisioned                   |    |

|      | integration with the electronic IC chip                                                   | 67 |

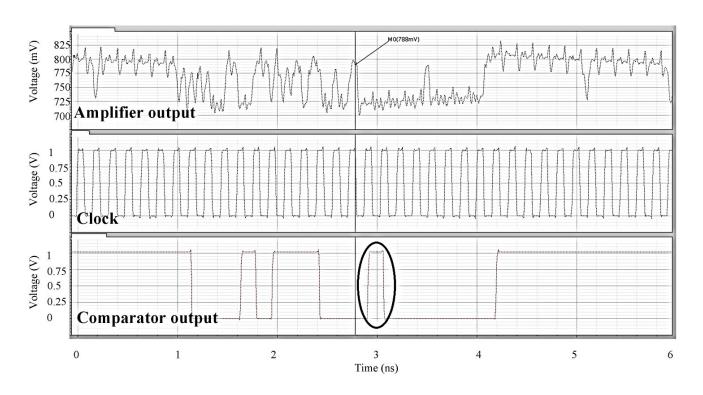

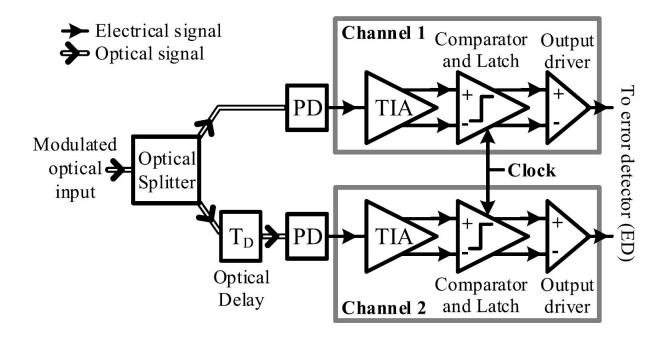

| 4.3  | The system-level details of the implemented two-channel receiver                          | 68 |

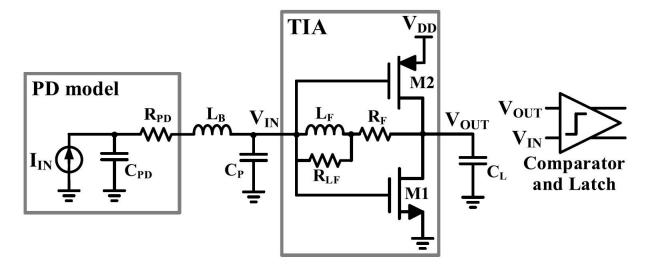

| 4.4  | The TIA circuit and its connections to the PD and comparator                              | 70 |

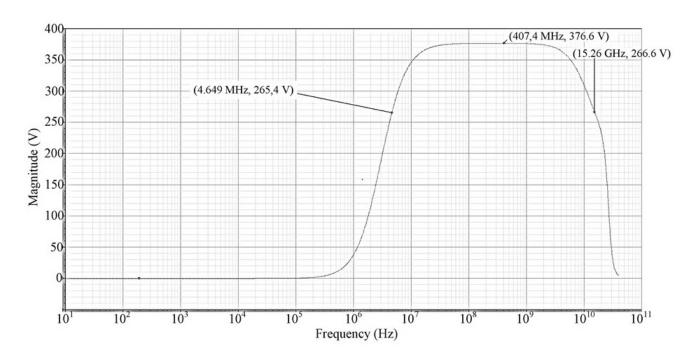

| 4.5  | The bode diagram for (a) $(V_{OUT}-V_{IN})/I_{IN}$ and $V_{OUT}$ / $I_{IN}$ ; (b)         |    |

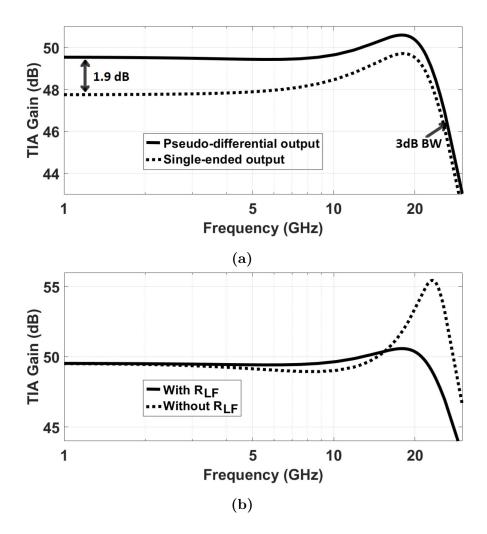

|      | $(V_{OUT} - V_{IN}) / I_{IN}$ with and without the damping resistor $R_{LF}$              | 73 |

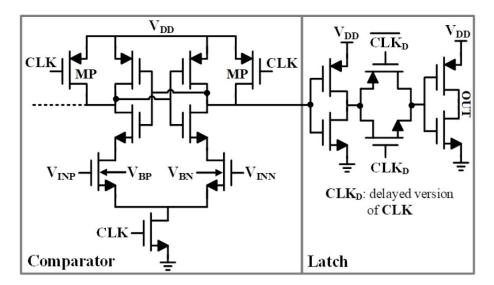

| 4.6  | The dynamic comparator and latch with offset-nulling signals $V_{BP}$ and $V_{BN}$ .      | 74 |

| 4.7  | Packaged chip micrograph of the receiver and its connections to                           |    |

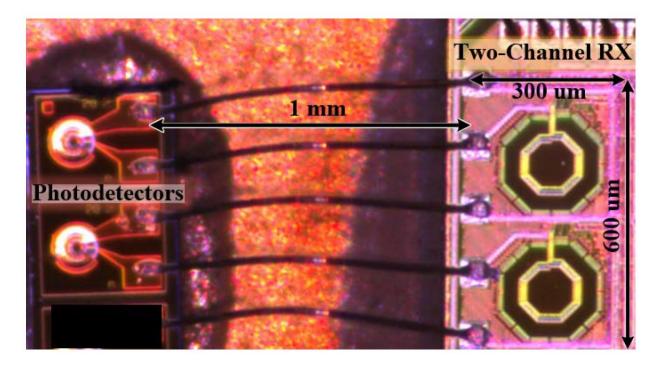

|      | photodetectors with 1 mm bondwires                                                        | 78 |

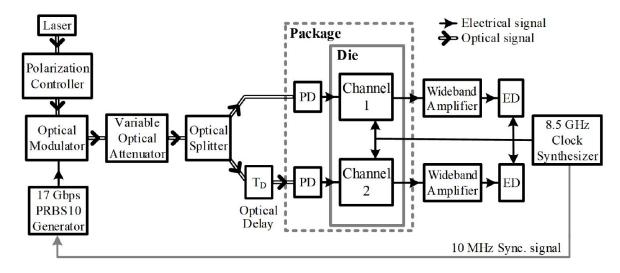

| 4.8  | Experimental test setup used to validate the optical receiver                             | 80 |

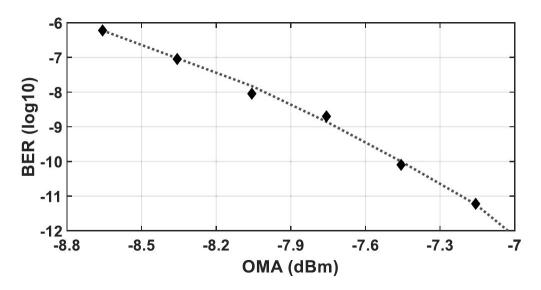

| 4.9  | Bit error rate (BER) for a 17 Gbps PRBS 10 optical input signal of the full               |    |

|      | receiver versus the input OMA at the input of the splitter and considering its            |    |

|      | 3.3 dB loss for the splitter                                                              | 81 |

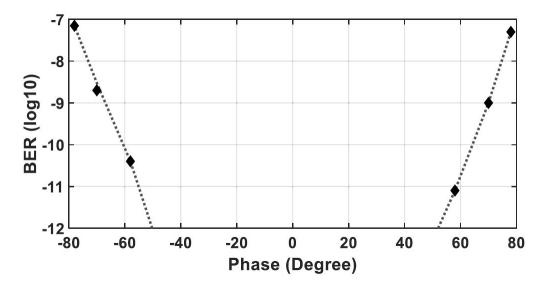

| 4.10 | Full receiver bathtub curve at a 17 Gbps input                                            | 81 |

List of Figures xviii

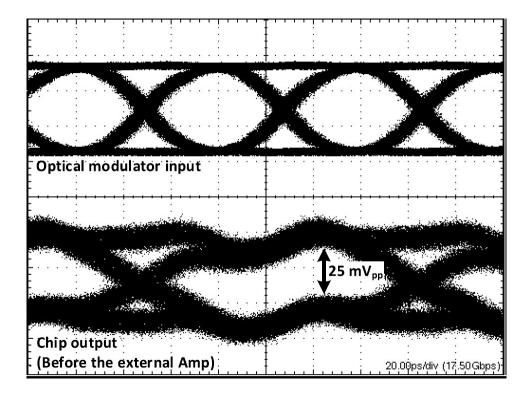

| 4.11 | The eye diagram of the input and output signals. Since the output signal                        |    |

|------|-------------------------------------------------------------------------------------------------|----|

|      | is single-ended and has a small amplitude, it is slightly distorted by some                     |    |

|      | common-mode noise                                                                               | 82 |

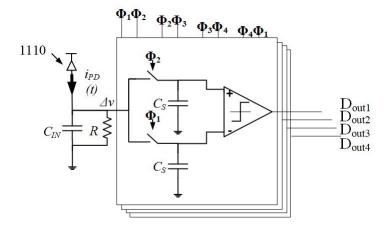

| 5.1  | Simplified integrating front-end receiver architecture with the four clock                      |    |

|      | phases $\Phi_1$ to $\Phi_4$                                                                     | 90 |

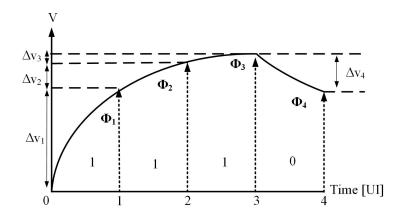

| 5.2  | Voltage at the input of the sampling circuit when the sequence 1110 is received.                |    |

|      | $\Delta v_x$ (x = 1,2,3,4) is the voltage difference between two consecutive samples.           | 91 |

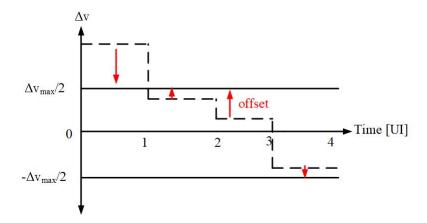

| 5.3  | Basic operation of the dynamic offset modulation (DOM) in the receiver to                       |    |

|      | compensate for CID. The red arrows indicate the offset generated by the                         |    |

|      | DOM circuit to compensate the $\Delta v$ shown in Fig. 5.2 and clamps the voltage               |    |

|      | difference to $\pm (\Delta v_{max})/2$                                                          | 91 |

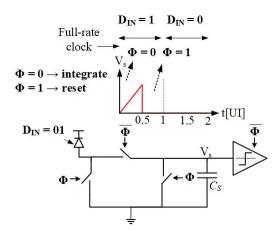

| 5.4  | Resettable receiver architecture operation and timing diagram showing the                       |    |

|      | integration for 0.5 UI and reset for 0.5 UI                                                     | 93 |

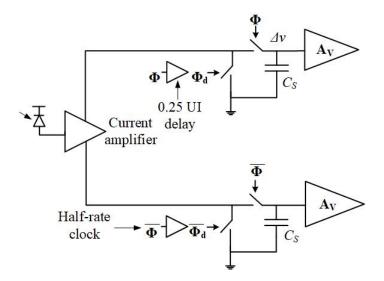

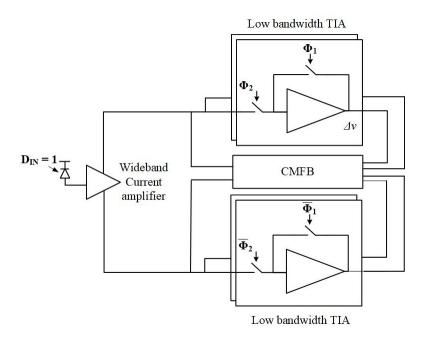

| 5.5  | Current-amplifier-based receiver architecture showing two interleaved paths                     |    |

|      | and sampling using two phases $(\Phi, \overline{\Phi})$ and a delayed version of the two phases |    |

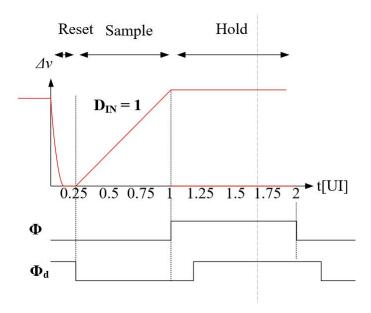

|      | $(\Phi_d, \overline{\Phi_d}))$                                                                  | 94 |

| 5.6  | Timing and operation of the current-amplifier-based receiver showing the reset                  |    |

|      | (0.25 UI), sample (0.75 UI), and hold phases (1 UI)                                             | 95 |

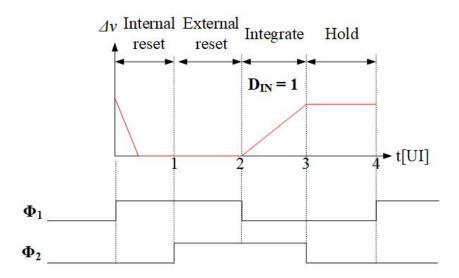

| 5.7  | Integrate-and-dump receiver showing four interleaved paths. It utilizes four                    |    |

|      | clock phases $(\Phi_1, \Phi_2, \overline{\Phi_1}, \overline{\Phi_2})$                           | 96 |

List of Figures xix

| 5.8  | Timing and operation of the of the integrate-and-dump receiver showing the                  |      |

|------|---------------------------------------------------------------------------------------------|------|

|      | four phases: internal reset, external reset, integrate, and hold                            | 96   |

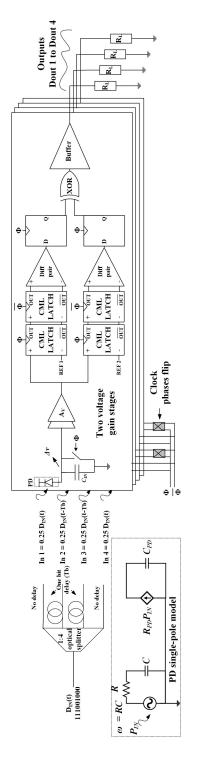

| 5.9  | Block diagram of the four proposed sub receivers and connection to the optical              |      |

|      | blocks with the delay scheme used. A single pole PD model is shown in the                   |      |

|      | inset                                                                                       | 98   |

| 5.10 | Timing diagram showing the operation of the receiver and the two phases of                  |      |

|      | operation                                                                                   | 99   |

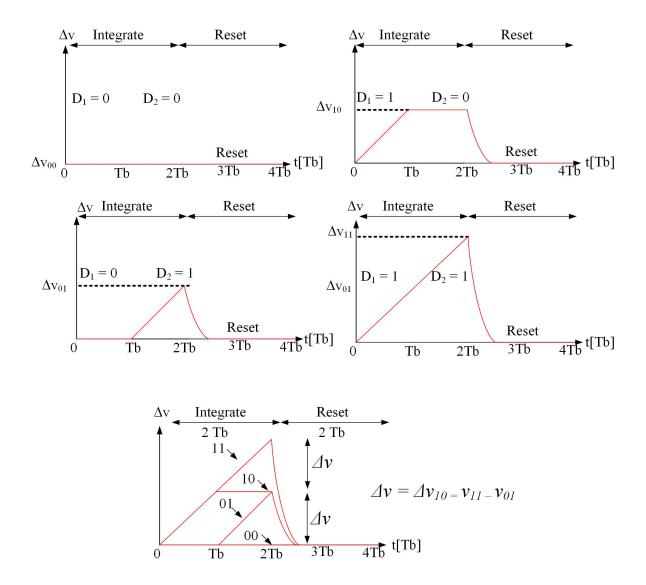

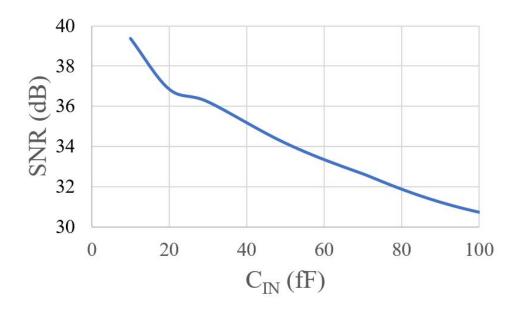

| 5.11 | Voltage integration $(\Delta v)$ at the front-end for all possible input values when        |      |

|      | the bandwidth of the photodetector is higher than 0.7 of the data-rate. The                 |      |

|      | bottom part shows an overlay of all $\Delta v$ possibilities                                | 101  |

| 5.12 | $\Delta v$ when the bandwidth of the photodetector is lower than 0.7 of the data-rate       | .102 |

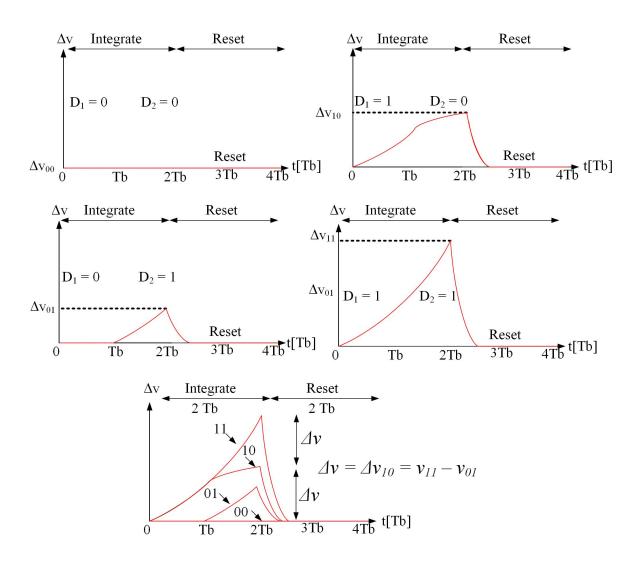

| 5.13 | The ratio of $\Delta v_{01}/\Delta v_{0.75T_b}$ vs photodetector bandwidth (in terms of bit |      |

|      | duration) in the case of the proposed receiver over that of the                             |      |

|      | current-amplifier-based receiver                                                            | 106  |

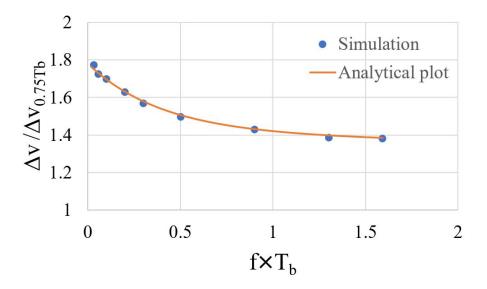

| 5.14 | Simulated SNR versus $\mathcal{C}_{IN}$ showing improvement with a smaller capacitance.     | 109  |

| 5.15 | Detailed circuit implementation of one of the four sub receivers in the proposed            |      |

|      | receiver. The input is wire bonded to a photodetector                                       | 111  |

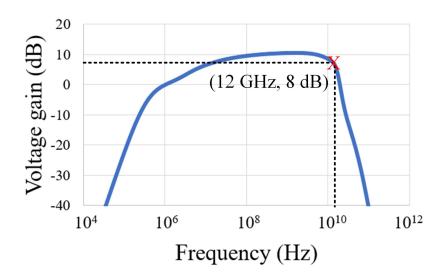

| 5.16 | AC simulation gain of the amplifier stages                                                  | 113  |

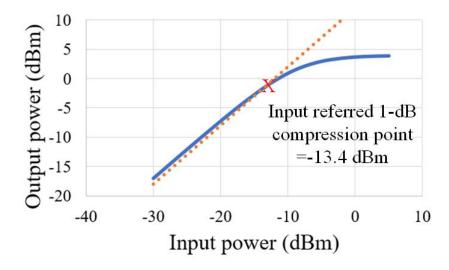

| 5.17 | The output power of the two amplifier stages versus the input power. The                    |      |

|      | input-referred 1-dB compression point is -13.4 dBm                                          | 113  |

List of Figures xx

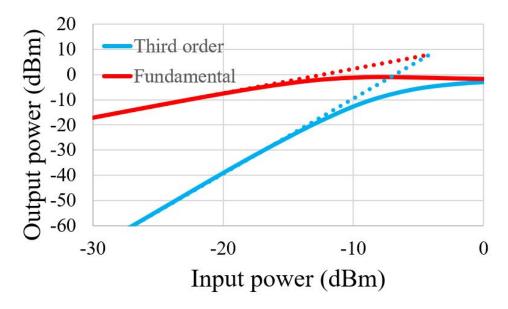

| 5.18 | Two-tone test showing the fundamental and the third-order harmonic powers.    |     |

|------|-------------------------------------------------------------------------------|-----|

|      | The IIP3 is at -4.15 dBm                                                      | 114 |

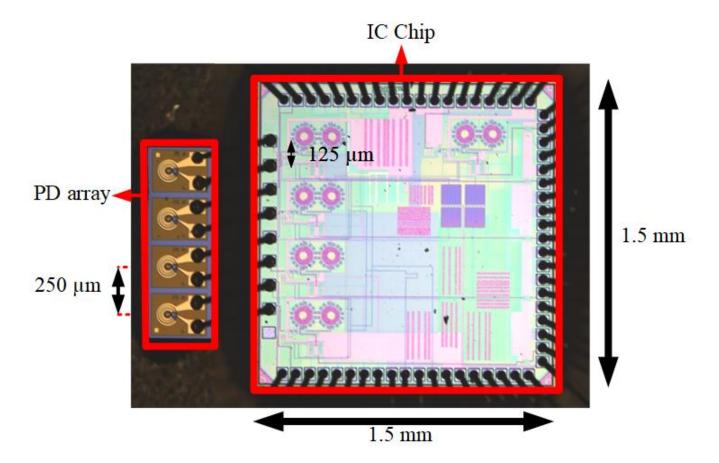

| 5.19 | Micrograph of the fabricated chip occupying 1.5 mm $\times$ 1.5 mm and wire-  |     |

|      | bonded to a 1 $\times$ 4 PD array with a 250 $\mu m$ pitch                    | 115 |

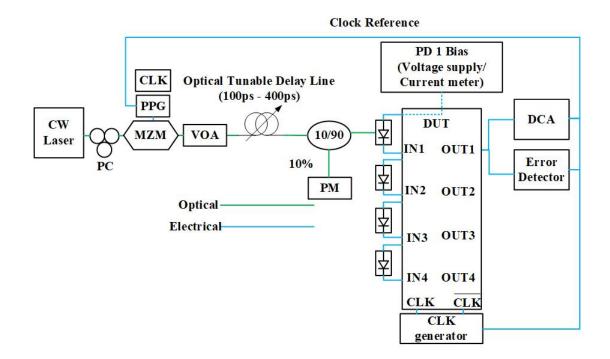

| 5.20 | Single sub receiver measurements setup                                        | 117 |

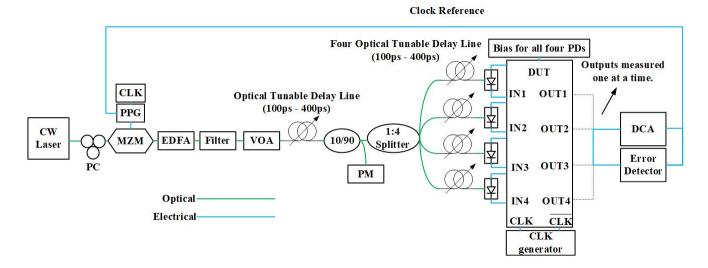

| 5.21 | Full system measurement setup                                                 | 118 |

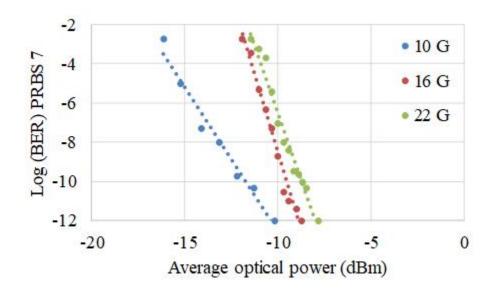

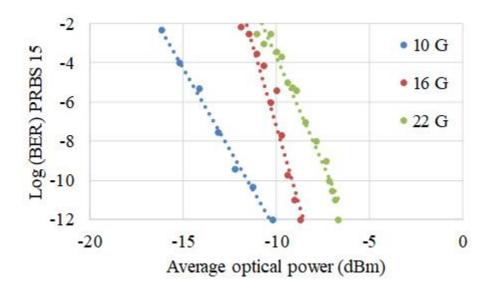

| 5.22 | BER measurements for PRBS 7 input                                             | 119 |

| 5.23 | BER measurements for PRBS 15 input                                            | 119 |

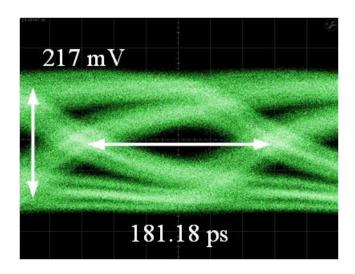

| 5.24 | 5.5 Gb/s output quarter-rate eye diagram                                      | 120 |

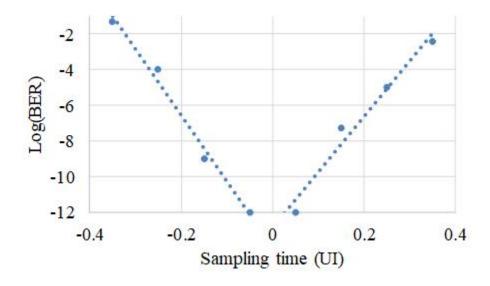

| 5.25 | Bathtub measurements at 22 Gb/s                                               | 120 |

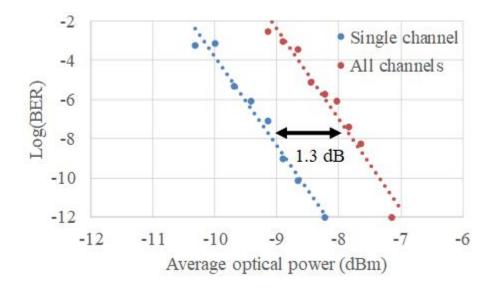

| 5.26 | BER curve comparing single channel operation with full system operation and   |     |

|      | crosstalk penalty at 22 Gb/s and with a PRBS 7 sequence                       | 121 |

| 5.27 | Layout of a proposed split-delay SiP structure including a grating coupler,   |     |

|      | three directional couplers acting as power splitters, two one-bit delay lines |     |

|      | and four photodetectors                                                       | 130 |

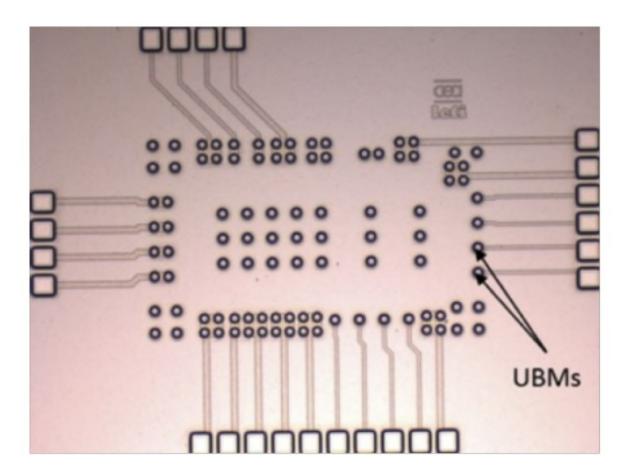

| 5.28 | SiPh chip with Under Bump Metallization (UBMs) used to connect to the IC      |     |

|      | chip in [48]                                                                  | 131 |

| 5.29 | Electronically tunable delay lines consisting of a ring resonator and an MZI  |     |

|      | delay elements [29]                                                           | 132 |

List of Figures xxi

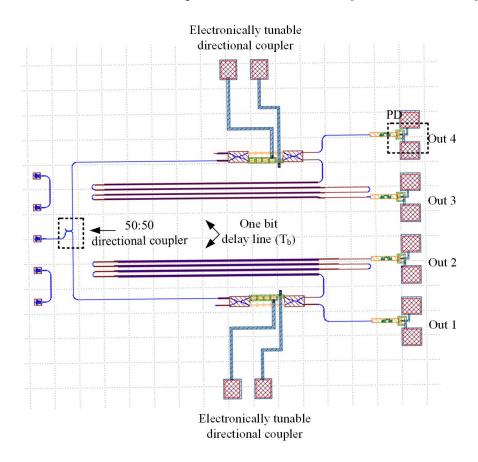

| 5.30 | Layout of a proposed split-delay SiP with directional couplers to ensure equal          |         |

|------|-----------------------------------------------------------------------------------------|---------|

|      | power at the output                                                                     | 133     |

| 6.1  | (a) Layout of the fabricated antenna. (b) Stack layers of the AMF SiP                   |         |

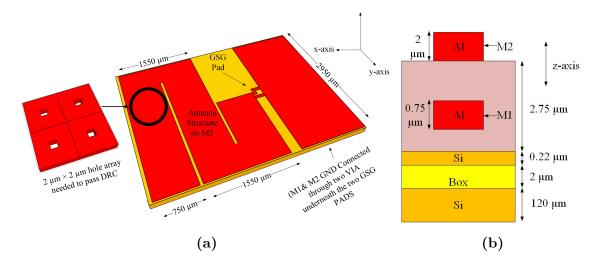

|      | fabrication process used to fabricate the antenna                                       | 138     |

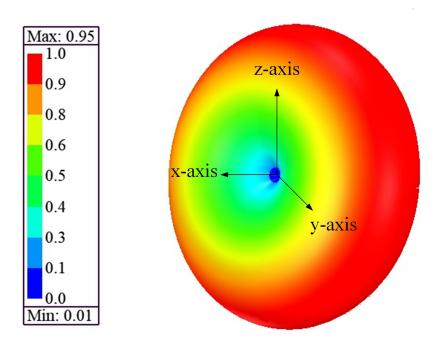

| 6.2  | The simulated donut-shaped gain of the antenna perpendicular to the plane               |         |

|      | of the antenna. This gain is valid in the far region of operation                       | 141     |

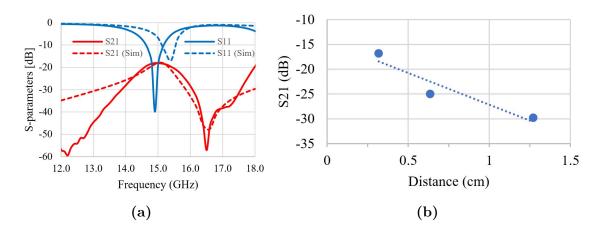

| 6.3  | (a) Measured and simulated (Sim) S-parameters with the antennas placed                  |         |

|      | $0.3175~\mathrm{cm}$ (0.125") apart. (b) Measured peak S21 at 15 GHz at three different |         |

|      | distances                                                                               | 143     |

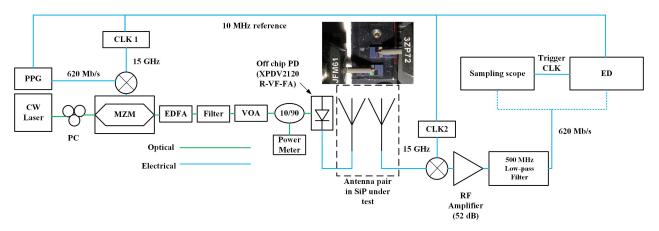

| 6.4  | Measurements setup for inter-chip communication with an external                        |         |

|      | photodetector as a transmitter directly driving the antenna. GSG probes                 |         |

|      | were used to drive the antennas as shown above the antenna pair symbol                  | 145     |

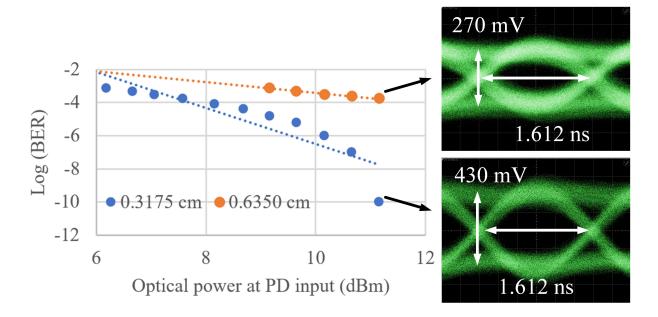

| 6.5  | Inter-chip antenna measured BER and eye diagrams curve for two different                |         |

|      | distances of antenna                                                                    | 146     |

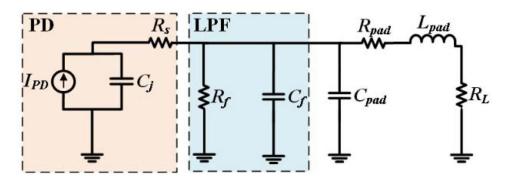

| 7.1  | Schematic of the circuit model for the designed RC low pass filters. Dashed             |         |

|      | boxes outline the PD and LPF configurations                                             | 152     |

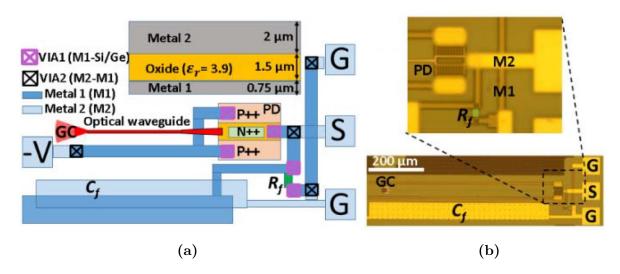

| 7.2  | (a) Cross-section view of the MIM capacitor and layout view of the LPF                  |         |

|      | structure (GC: grating coupler, PD: photodiode, M1: Metal 1, M2: Metal 2).              |         |

|      |                                                                                         | . 1 = 4 |

|      | (b) Micrograph of the RC filter structure in an active silicon photonics process        | 104     |

List of Figures xxii

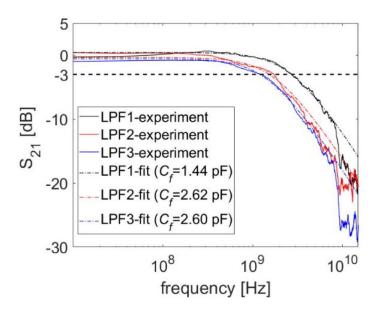

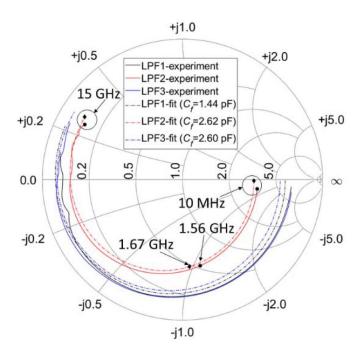

| 7.3 | Measured and fitted $S_{21}$ parameter using the lumped model shown in Fig. 7.1          |     |

|-----|------------------------------------------------------------------------------------------|-----|

|     | and the parameters values in Table 7.1 for chip no. 3 at 2 V reverse bias                | 158 |

| 7.4 | Measured and fitted $S_{22}$ parameter using the lumped model shown in Fig. 7.1          |     |

|     | and the parameters values in Table 7.1 for chip no. 3 at 2 V reverse bias                | 159 |

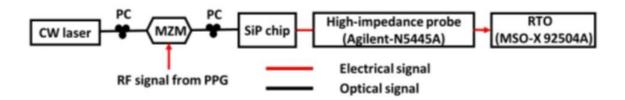

| 8.1 | Schematic diagram of the moving average structure and the cross-section of               |     |

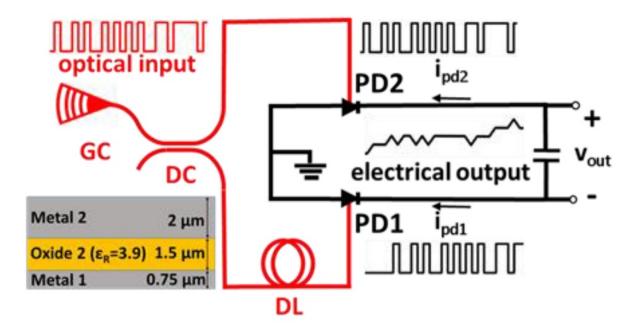

|     | the MIM capacitors in the silicon photonics process                                      | 165 |

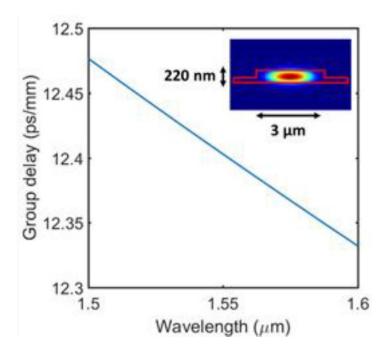

| 8.2 | Calculated group delay per mm for 3 $\mu\mathrm{m}\times$ 220 nm low-loss rib waveguides |     |

|     | used for the delay (DL). The inset shows a simulation of the cross-section of            |     |

|     | the fundamental mode                                                                     | 167 |

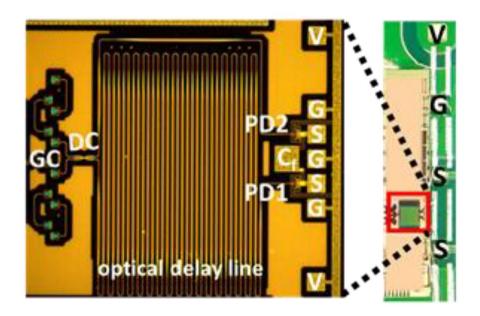

| 8.3 | Micrograph of the wire-bonded silicon photonic die on the PCB with an                    |     |

|     | enlarged view of the fabricated moving average structure. GC: grating                    |     |

|     | coupler; DC: directional coupler; DL: delay line; PD1, PD2: photodiodes; G:              |     |

|     | ground pads; S: signal pads; V: DC voltage pads; $C_f$ : integrating capacitor           | 168 |

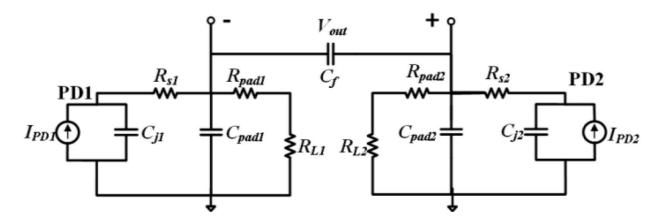

| 8.4 | Schematic diagram of the moving average structure including the parasitics               |     |

|     | and the high-impedance probe input resistance where $R_L=100~k\Omega$ is the             |     |

|     | high-impedance probe input impedance, $C_f = 200 \ fF$ is the moving average             |     |

|     | integrator, $C_{j1} = C_{j2} = 15 \ fF$ are the photodiode junction capacitances,        |     |

|     | $R_{s1}=R_{s2}=125~\Omega$ are the photodiodes series resistances, and $=C_{pad1}=$      |     |

|     | $C_{pad2} = 15 \ fF$ are the pads capacitance                                            | 170 |

| 8.5 | Simulation results for random sequences (a) at 2.5 Gbps with two decision-                        |

|-----|---------------------------------------------------------------------------------------------------|

|     | making levels of $j_1$ and $j_2$ , (b) at 5 Gbps with three decision-making levels of             |

|     | $m_1$ , $m_2$ , and $m_3$ , and (c) at 10 Gbps with five decision-making levels of $n_1$ ,        |

|     | $n_2$ , $n_3$ , $n_4$ , and $n_5$ . The insets show the corresponding simulated eye diagrams. 170 |

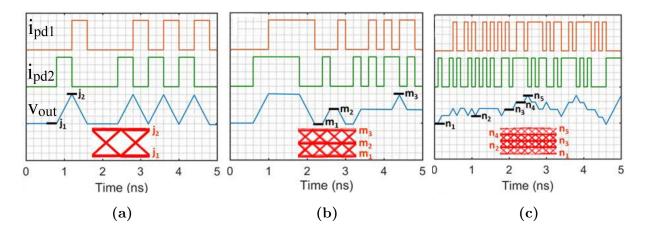

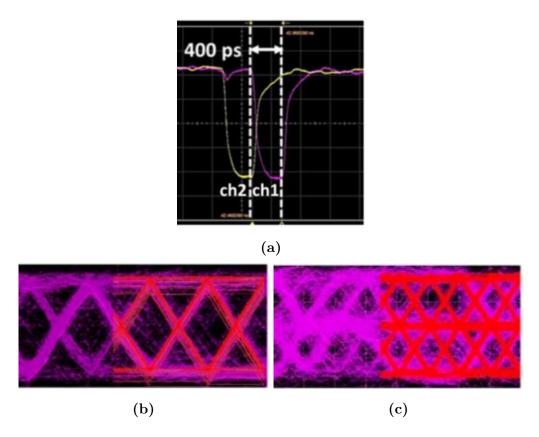

| 8.6 | Experimental setup for the characterization of the moving average integrator. 172                 |

| 8.7 | (a) Experimental validation of the 400 ps optical delay line (length of 32.3                      |

|     | mm at 1550 nm) using 50 $\Omega$ impedance GSG probes. Experimental versus                        |

|     | simulation results: the purple graphs are the measured output and the                             |

|     | overlapped red graph is the simulated output at (b) 2.5 Gbps and (c) 5 Gbps. 173                  |

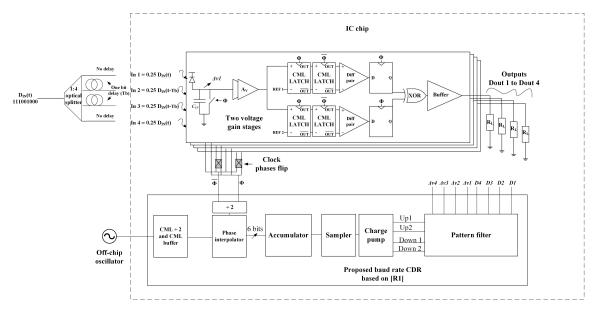

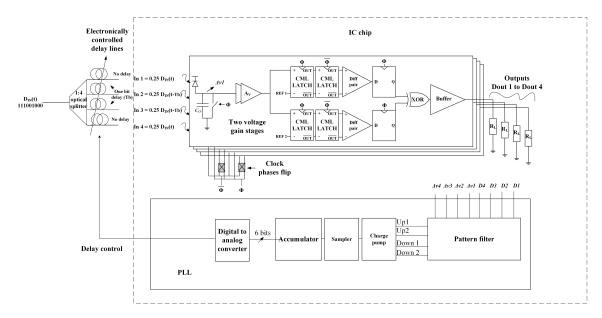

| 9.1 | A CDR that could be used with the proposed receiver in [7] based on [34] 178                      |

| 9.2 | A DLL that could be used with the proposed receiver based on [34] 179                             |

|     |                                                                                                   |

# List of Tables

| 3.1 | Performance summary and comparison                                    | 60  |

|-----|-----------------------------------------------------------------------|-----|

| 4.1 | Component values used in Fig. 4.4 and to plot Fig. 4.5                | 72  |

| 4.2 | Performance summary and comparison                                    | 83  |

| 5.1 | Performance summary and comparison (part 1)                           | 125 |

| 5.2 | Performance summary and comparison (part 2)                           | 126 |

| 7.1 | equivalent circuit parameters                                         | 156 |

| 7.2 | Measured versus designed capacitance (pF) and resistance ( $\Omega$ ) | 158 |

| 7.3 | Filter cut-off frequencies (GHz)                                      | 160 |

# List of Acronyms

AC Alternating current

ADC Analogue to digital converter

**BER** Bit error rate

**BOX** Buried oxide

**BPG** Bit pattern generator

**CID** Consuctive identical bits

**CMOS** Complementary metal oxide semiconductor

CML Current mode logic

**CW** Continuous wave

**ED** Error detector

**EDFA** Erbium-doped fiber amplifier

**DCA** Digital communication analyzer

**Demux** Demultiplexing

**DFE** Decision feedback equalizer

**DOM** Dynamic offset modulation

**DRC** Design rule check

**FEC** Forward error correction

**ISI** Intersymbol interference

IC Integrated circuit

I/O Input-output

LA Limiting amplifier

MIM Metal insulator metal

MOSFET Metal oxide semiconductor field effect transistor

MUX Multiplexer

MZI Mach-Zehnder interferometer

MZM Mach-Zehnder modulator

**NF** Noise figure

NRZ Non-return-to-zero

**ODL** Optical delay line

OOK On-off keying

OMA Optical modulation amplitude

PAM Pulse amplitude modulation

PC Polarization controller

PCB Printed circuit board

**PD** Photodetector

PLL Phase-locked loop

**PPG** Pulse pattern generator

PRBS Pseudorandom binary sequence

**RF** Radio frequency

RX Receiver

**RZ** Return-to-zero

SiGe Germanium on Silicon

SiP Silicon photonics

**SNR** Signal-to-noise ratio

**SOI** Silicon on insulator

**TIA** Transimpedance amplifier

Tx Transmitter

VOA Variable optical attenuator

**XOR** Exclusive OR boolean logic

## Chapter 1

## Introduction

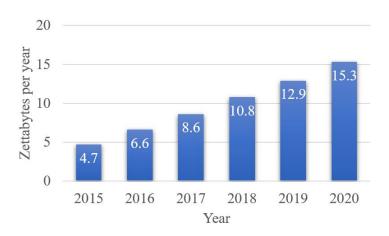

Over the past few years, internet traffic has increased significantly and was projected to increase from 4.7 Zettabyte in 2015 to 15.3 Zettabyte in 2020 as shown in Fig. 1.1 [1]. This increase is caused by the expanding use of high definition online streaming, cloud storage, cloud computing, social media, and gaming streaming services among other data-hungry services. This projection does not account for the on-going pandemic that would increase data usage due to more people working from home and having more time to use online services.

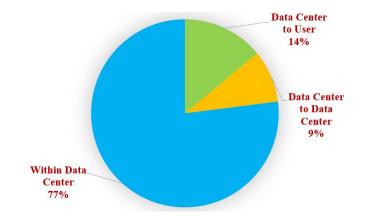

Interestingly, most data traffic, 77 %, takes place within the data center as shown in Fig. 1.2 [1]. To support traffic of this magnitude within data centers, optical interconnects offer an attractive alternative to copper interconnects that suffer from many limitations at high-speed. In order to accommodate these optical interconnects within data-centers,

Fig. 1.1: Data traffic per year in data centers [1].

Fig. 1.2: Data traffic breakdown by destination [1].

high-speed and energy-efficient optical receivers are required.

### 1.1 Motivation

The advent of optical interconnects in data centers requires the design of energy-efficient optoelectronic transceivers. In the near term, to improve the bandwidth and reduce the power consumption of optoelectronic transceivers, optical I/O solutions must integrate

electronic and photonic elements in the package [2]. This integration provides an opportunity where photonic elements can be used to perform optical data processing potentially eliminating or replacing certain electronic circuit blocks in optoelectronic transceivers and improving their overall energy efficiency. For example, in [2], modulators, waveguides, and photodetectors are integrated with a CMOS transceiver. In [3], an add/drop wavelength filter is integrated with a CMOS receiver. In [4], an optical wavelength interleaver is integrated with a CMOS transceiver.

Silicon photonics is a logical candidate to realize this approach as its manufacturing leverages the existing CMOS technology infrastructure.

This motivates the co-design of electronics and photonics to meet the requirements of optical interconnects in data centers. It also motivates exploring the feasibility of developing passives in silicon photonics that are usually found on the electronic integrated circuit side as it may lead to the development of better integrated co-designed electronic/optical systems

### 1.2 Thesis objectives

The primary objective of this thesis is to develop an energy-efficient, high-speed, high-sensitivity optical receiver that leverages silicon photonics to improve the performance of the system. More specifically, the thesis will attempt to validate the following two hypotheses:

Clock generation for optical receivers can be constructed from optical delay lines instead

of electronic delay lines to achieve less power consumption and higher energy efficiency.

• An optical receiver can be constructed in silicon that uses a low-bandwidth front-end electronic circuit of less than 0.7×data-rate to achieve the given data-rate throughput.

To this goal, three integrated circuits were developed and measured. The first receiver in [5] explores the potential of using silicon photonic delay lines to replace quadrature clock phase generation circuits in optical receivers. The second receiver in [6] applies the same concept to a two clock phase optical receiver and simplifies the first design in an attempt to achieve better power consumption and sensitivity. The third receiver in [7] employs the same concept but also presents a novel low-bandwidth front-end to boost the speed of the receiver.

A secondary objective is to explore the potential of implementing passive components in the silicon photonic platforms. This exploration may lead to better co-designed optical/electronic systems and reduced cost. More specifically, the thesis will attempt to validate the following two hypotheses:

- An on-chip antenna can be integrated in a silicon photonic fabrication technology.

- An RC filter and moving average filter can be integrated in a silicon photonic fabrication technology.

To validate this, three different implementations are explored. The first is an on-chip antenna in the silicon photonics platform. This studies the feasibility of doing wireless RF inter-chip data transmission in the silicon photonics platform. The second implementation is a low-pass filter driven by a photodetector. This implementation studies the idea of relocating bulky passives such as capacitors and resistors from the integrated circuit side to the silicon photonics platform to potentially save cost. Finally, the third implementation combined optical delay lines, photodetectors, and a capacitor to develop a moving average filter. A moving average filter in the silicon photonics platform may be valuable for the emerging low-bandwidth optical receivers and has the potential to enable the design of receivers with superior performance.

These objectives are summarized below:

- Develop optical receivers that leverage silicon photonics.

- Develop an optical receiver that uses silicon photonic delay lines to replace quadrature clock phase generation in optical receivers.

- Develop a single-phase optical receiver the leverages silicon photonics to simplify

the design which may lead to improved performance.

- Develop an optical receiver with a novel low-bandwidth integrating front-end that may lead to achieving higher data rates.

- Develop passives in the the silicon photonics platform to explore their potential. This

may enable the development of better integrated co-designed systems.

Develop an RF antenna in the silicon photonics platform and explore the possibility of inter-chip transmission.

- Develop an RC filter in the silicon photonics platform.

- Develop a moving average filter in silicon photonic that may prove valuable at the front-end of the emerging low-bandwidth optical receivers.

#### 1.3 Claim of Originality

The high-level engineering attempt to boost performance is the co-design and co-optimization of electronics and photonics. This design mentality allowed the proposed systems to achieve better performance than other receivers. The specific advances and conurbations are detailed below:

• Two optical receivers with conventional front-ends that leverage optical delay lines were developed. This novel technique simplifies clock phase generation in optical receivers to achieve improved energy efficiency and reduce clock generation power consumption. The first receiver, presented in chapter 3, is a first demonstration that used silicon photonic delay lines to replace clock phase generation circuits. While the silicon photonic delay lines were published by the group prior to the start of this Ph.D., the contribution presented in this thesis is the first demonstration of the IC

chip leveraging the optical delay lines. This is more of a demonstration of feasibility rather than an engineering advance attempt attempt since the design approach is an invention (patent no 9,917,650) and this PhD prototyped the novel front-end. The second receiver presented in chapter 4 is a simplified receiver that leverages optical delay lines to achieve a demultiplex-by-two operation. The engineering advance here is the simplicity of the design and the removal of the voltage gain stages. The result of this is the superior energy efficiency achieved by the receiver. Both receivers are demonstrated experimentally [5, 6]. The authors of [6] believe that the energy efficiency achieved of 156 fJ/bit is the best reported compared to the state-of-the-art.

- A novel optical receiver with a low-bandwidth two-bit integrating optical front-end was developed that in addition to leveraging optical delay lines for clock generation, employs a novel low-bandwidth front-end to achieve high-speed of operation. This third receiver, presented in chapter 6, utilizes an integrating front-end to achieve high-speed in the CMOS 65nm technology node. The engineering advance is the innovative integrating front-end described in the chapter. This receiver was verified through experimental measurements with a photodetector array [7] and achieves a speed of 22 Gb/s with an energy efficiency of 1.43 pJ/bit.

- An on-chip antenna in silicon photonics stack was developed and inter-chip was demonstrated for the first time in this stack. Antenna design, fabrication, and measurements are described in detail [8]. The antenna may be used for inter-chip

communication applications involving a central control unit or microprocessor and several optical receivers without the need for wire bonding.

- An RC filter and a moving average filter were developed in the silicon photonics platform. These two implementations allows for the relocation of some passives from the integrated chip side to the photonic chip side potentially saving cost and allows for better designed integrated systems. Both filters were designed, fabricated, and verified experimentally [9, 10]. The moving average filter and the low-pass filter are exploratory research ideas that could potentially be eventually integrated within the optical receiver. For example, the moving average filter could be used to replace the reset function in the receiver that is proposed in chapter 5.

- The passive structures in silicon photonics designs are not engineering advances that attempt to improve performance, but rather explorative and innovative designs that attempt to assess and measure the feasibility of passives in the SiPh platform.

#### 1.3.1 Publications and contributions of the author

The contents of this thesis are presented in several publications that include six journal articles, and one conference proceeding. The following is a list of publications and contributions of the author. The conference paper used in this thesis, [11], acts as a survey of electronic and optical delay lines and is presented in background section. Each of the

optical receivers is presented in a separate journal paper [5–7], and each of the three passives implemented in the silicon photonic stack is presented in a separate journal paper [8–10].

Additionally, the author authored and co-authored four additional conference publications not related to this thesis [12–15].

#### Peer-reviewed Journal Articles:

- [5] B. Radi, M. S. Nezami, M. Ménard, F. Nabki and O. Liboiron-Ladouceur, "A 12.5 Gb/s 1.93 pJ/bit Optical Receiver Exploiting Silicon Photonic Delay Lines for Clock Phases Generation Replacement," in IEEE Transactions on Circuits and Systems II: Express Briefs, doi: 10.1109/TCSII.2019.2952591 (Early access).

- B. Radi: Proposed the idea, designed and drew the layout of the receiver, performed all the measurement, and wrote the manuscript.

- M. S. Nezami: Assisted with the measurements.

- M. Ménard: Provided feedback, edited, and reviewed the manuscript.

- F. Nabki: Provided feedback, edited, and reviewed the manuscript.

- O. Liboiron-Ladouceur: Supervised the work, edited, and reviewed the manuscript.

- [6] M. Taherzadeh-Sani, B. Radi, M. S. Nezami, M. Ménard, O. Liboiron-Ladouceur and F. Nabki, "A 17 Gbps 156 fJ/bit Two-Channel Optical Receiver With Optical-Input

Split and Delay in 65 nm CMOS," in IEEE Transactions on Circuits and Systems I: Regular Papers, doi: 10.1109/TCSI.2020.2976197 (Early access).

- M. Taherzadeh-Sani: Designed and drew the layout of the receiver, performed measurements, and wrote the manuscript.

- B. Radi: Involved with the design and the measurements of the receiver. Assisted with drafting the manuscript.

- M. S. Nezami: Assisted with the measurements.

- M. Ménard: Provided feedback, edited, and reviewed the manuscript.

- O. Liboiron-Ladouceur: Provided feedback, edited, and reviewed the manuscript.

- F. Nabki: Supervised the work, edited, and reviewed the manuscript.

- [7] B. Radi, M. Taherzadeh-Sani, M. S. Nezami, F. Nabki, M. M'enard, and O. Liboiron-Ladouceur, "A 22 Gb/s time-interleaved low-power optical receiver with a two-bit integrating front-end," IEEE Journal of Solid-State Circuits (Accepted, ID: JSSC-19-0447.R2).

- B. Radi: Proposed the idea, designed and drew the layout of the receiver, performed all the measurements, and wrote the manuscript.

- M. S. Nezami: Assisted with the measurements.

- M. Taherzadeh-Sani: Provided feedback on the design and assisted with revisions.

- F. Nabki: Provided feedback, edited, and reviewed the manuscript.

- M. Ménard: Provided feedback, edited, and reviewed the manuscript.

- O. Liboiron-Ladouceur: Supervised the work, edited, and reviewed the manuscript.

- [8] B. Radi, A. S. Dhillon and O. Liboiron-Ladouceur, "Demonstration of Inter-Chip RF Data Transmission Using On-Chip Antennas in Silicon Photonics," in IEEE Photonics Technology Letters, vol. 32, no. 11, pp. 659-662, 1 June, 2020, doi: 10.1109/LPT.2020.2991118.

- B. Radi: Proposed the idea, designed, and drew the layout of the antenna, performed all the measurements, and wrote the manuscript.

- A. S. Dhillon: Assisted with the measurements.

- O. Liboiron-Ladouceur: Supervised the work, edited, and reviewed the manuscript.

- [9] M. S. Nezami, B. Radi, A. Gour, Y. Xiong, M. Taherzadeh-Sani, M. Ménard, F. Nabki, and O. Liboiron-Ladouceur, "Integrated RF Passive Low-Pass Filters in Silicon Photonics," in IEEE Photonics Technology Letters, vol. 30, no. 23, pp. 2052-2055, 2018, doi: 10.1109/LPT.2018.2875895.

- M. Sanadgol Nezami: Measured the filter and wrote the manuscript.

- B. Radi: Assisted with the design, with measurements, and with the drafting of the manuscript.

- A. Gour: Assisted with the design.

- Y. Xiong: Assisted with the design.

- M. Taherzadeh-Sani: Provided feedback on the manuscript.

- M. Ménard: Provided feedback, edited, and reviewed the manuscript.

- F. Nabki: Provided feedback, edited, and reviewed the manuscript.

- O. Liboiron-Ladouceur: Supervised the work, edited, and reviewed the manuscript.

- [10] M. S. Nezami, B. Radi, M. Taherzadeh-Sani, Y. Xiong, M. Ménard, F. Nabki, and O. Liboiron-Ladouceur, "A high-speed moving average integrator in silicon photonics for TIA-less receivers," IEEE Photonics Technology Letters (Accepted, ID: PTL-37154-2020.R1).

- M. Sanadgol Nezami: Measured the filter and wrote the manuscript.

- B. Radi: Generated the idea, assisted with the design, with measurements, and with the drafting of the manuscript.

- Y. Xiong: Designed the filter.

- M. Taherzadeh-Sani: Provided feedback on the manuscript.

- M. Ménard: Provided feedback, edited, and reviewed the manuscript.

- F. Nabki: Provided feedback, edited, and reviewed the manuscript.

- O. Liboiron-Ladouceur: Supervised the work, edited, and reviewed the manuscript.

#### Peer-reviewed Conference Articles:

[11] B. Radi, A. S. Dhillon, and O. Liboiron-Ladouceur, "Towards integrated rf photodetector-antenna emitters in silicon photonics," in 2020 IEEE Photonics Conference (IPC) (Accepted, Paper ID = 147, Conference date: September 28th – October 1st, 2020).

- B. Radi: Wrote the manuscript.

- A. S. Dhillon: Assisted with the measurements.

- O. Liboiron-Ladouceur: Supervised the work, edited, and reviewed the manuscript.

- [16] B. Radi and O. Liboiron-Ladouceur, "A survey of optical and electronic delay lines with a case study on using optical delay lines in 65nm CMOS optical receivers," in 2020 IEEE International Midwest Symposium on Circuits and Systems(MWSCAS) (Accepted, Paper ID = 3226, Conference date: August 9th August 12th, 2020).

- B. Radi: Wrote the manuscript.

- O. Liboiron-Ladouceur: Supervised the work, edited, and reviewed the manuscript.

#### Peer-reviewed Conference Articles not related to this thesis:

[12] Y. Xiong, F. G. de Magalhães, B. Radi, G. Nicolescu, F. Hessel, and O. Liboiron-Ladouceur, "Towards a fast centralized controller for integrated silicon photonic multistage MZI-based switches," in 2016 Optical Fiber Communications

Conference and Exhibition (OFC), pp. 1–3, 2016.

- [13] V. E. Paul, B. Radi, V. Tolstikin, and O. Liboiron-Ladouceur, "A technology-based comparative study for the optoelectronic integration of optical front-ends," in 2016 Photonics North (PN), pp. 1–1, 2016.

- [14] B. Radi, V. E. Paul, V. Tolstikhin, and O. Liboiron-Ladouceur, "Comparative study of optoelectronics receiver front-end implementation in InP, SiGe, and CMOS," in 2016 IEEE Photonics Conference (IPC), pp. 222–223, 2016.

- [15] H. R. Mojaver, A. Das, B. Radi, V. Tolstikhin, K.-W. Leong, and O. Liboiron-Ladouceur, "Scalable SOA-based lossless photonic switch in InP platform," in Optical Interconnects 2020 (Accepted, Paper ID = 25, Conference date: September 27th Oct 1st, 2020).

# 1.4 Thesis Organization

This thesis consists of two themes: the co-design of electronics and photonics for optical receiver design and the implementation of passives in silicon photonics. Chapter 2 reviews some background information necessary to understand the contents of this thesis. The first theme is covered in Chapter 3, Chapter 4, and Chapter 5. Chapter 3 describes the design of a 12.5 Gb/s demux-by-four receiver with a conventional front-end that leverages silicon photonic delay lines for clock phase generation. Chapter 4 describes a 17 Gb/s demux-by-

two receiver that leverages the optical delay lines to simplify the receiver and the clocking to achieve superior energy efficiency. Chapter 5 describes a novel optical receiver with a low-bandwidth two-bits integrating front-end and achieves a speed of 22 Gb/s. All three receivers are implemented in CMOS 65 nm and are verified experimentally. The second theme is covered in Chapter 6, Chapter 7, and Chapter 8. Chapter 6 describes the design of a 15 GHz RF antenna in silicon photonics. This chapter also describes, for the first time, the demonstration of inter-chip data transmission in silicon photonics. Chapter 7 presents the design of a low-pass RC filter in the silicon photonics process. Chapter 8 is an extension of chapter 7 and describes the implementation of a moving average filter in silicon photonics using delay lines and on-chip capacitor. Finally, chapter 9 proposes suggested future work and concludes the thesis.

# Chapter 2

# Background

This chapter presents some background information necessary to understand and appreciate the contents of this thesis. The first section provides general and basic information about the silicon photonics process. The second section is a survey of commonly used electronic and an overview of optical delay lines that will be used in the next three chapters. The third section is a more detailed look at passive optical delay lines and provides information about demultiplexing in optical receivers. Finally, the fourth section gives a general overview of optical receiver design and challenges.

# 2.1 An overview of silicon photonics

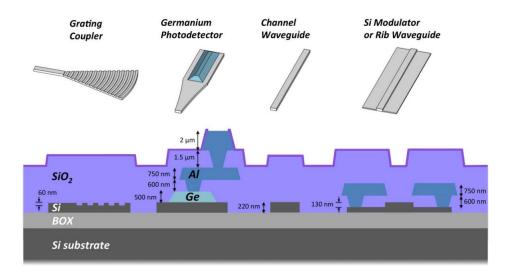

This section provides a brief overview of the silicon photonics process. The silicon photonics process by Advanced Micro Foundry (AMF) (formerly IME) is shown in Fig. 2.1 with some

Fig. 2.1: Silicon photonics process cross-section [17].

device examples [17].

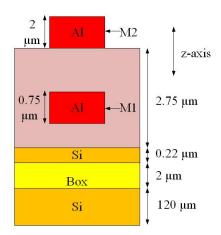

The process consists of a silicon-on-insulator (SOI) wafer with a 220 nm silicon layer for devices and 2  $\mu$ m buried oxide (BOX) layer. The device layer can be etched at 0 nm, 90 nm, and 160 nm in addition to the standard etching at 220 nm. The process has 6 implants for optical modulators (P++, P+, P, N++, N+, N) and Germanium deposition and implanting for photodetectors. The process also provides contact vias and two Aluminum layers.

The stack of the Silicon Photonics process is shown in Fig. 2.2. The process consists of a Si substrate that is 120  $\mu$ m thick. On top of the substrate, there is a silicon oxide layer (BOX) that is 2  $\mu$ m thick, followed by a 220 nm Si layer. This layer can be etched to build waveguides and grating couplers or implanted to make different components such as photodetectors. Ge can be deposited on top of this Si layer to complete the structures of

Fig. 2.2: Silicon photonics process cross-section [17].

the photodetector. The two metal layers can be connected to the 220 nm Si layer and each other using vias. The metal layers are covered with oxide cladding.

The process allows for the fabrication of many devices such as the ones shown in Fig. 2.1.

A brief description of some of the devices that can be fabricated in the silicon photonics process is provided next.

Grating couplers is a structure that allows the light to be coupled in and out of the chip. Grating couplers are built by alternating the etching height which essentially means periodically alternating the refractive index. This will lead to strong frequency (or wavelength) selection and the incident light will be refracted along the coupler and eventually be guided along a waveguide or from waveguide to free space.

Channel waveguides and rib waveguides are used to guide light on the silicon photonic chip and serve as interconnects between different blocks on the chip. These waveguides can have different insertion loss depending on the width and the structure used. For example,

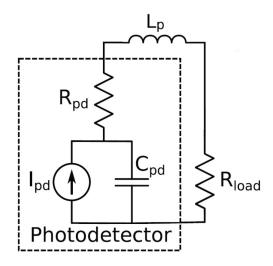

Fig. 2.3: Photodetector model in [19].

the insertion loss in the waveguides used in [18] is 3 dB/cm for 220 nm  $\times$  500 nm channel waveguides and 0.2 dB/cm for 220 nm  $\times$  3  $\mu$ m waveguides. These waveguides can be used to build passive optical delay lines as detailed later in the chapter.

Photodetectors are key components used at the interface of optical chips and electronic chips. Photodetectors are used to convert light into current through the absorption of photons. They are characterized by their operating wavelength, bandwidth, and responsivity. A photodetector, a model of which is shown in Fig. 2.3, is usually modeled as a current source,  $I_{pd}$ , in parallel with a junction capacitance,  $C_{pd}$ , used to represent the capacitance of the reverse-biased PN junction. The parallel combination of the current source and junction capacitance is in series with a series resistance,  $R_{pd}$ , that represents the effective resistance of the junction. Finally, an inductor,  $L_p$ , is used to represent the peaking inductor (if used) and any bond wire parasitic inductance.

The responsivity, R, of the photodetector relates the photocurrent generated to the incident optical power,  $P_{opt}$ , incident as shown in equation 2.1.

$$I_{pd} = R \times P_{opt} \tag{2.1}$$

Electro-optic modulators are devices used to modulate the continuous light by applying a voltage to a certain region of the device. The applied voltage will result in a change in the refractive index and the change in the refractive index leads to phase change. The phase change can be made out to be 0 degrees or 180 degrees by applying different voltages. It is then possible to combine this modulated signal with a copy of the same signal to achieve on-off keying modulation.

Directional couplers are devices that can be used as optical power splitters. Directional couplers are created by placing two waveguides with a certain length in close proximity. The fields will transfer from one waveguide to the other as they travel along the waveguide. By choosing the proper length, the amount of field energy transferred can be effectively controlled. This sets the power splitting ratio.

Finally, Y-branches are passive optical devices used to split the optical power in half.

This section provided a brief overview of the silicon photonic process and some of the devices that could be implemented. Of importance to this thesis are waveguides, photodetectors, directional couplers, and Y-branches. The following sections provide more details about optical delay lines that are built using waveguides.

#### 2.1.1 Motivation for passives electronics in Silicon Photonics

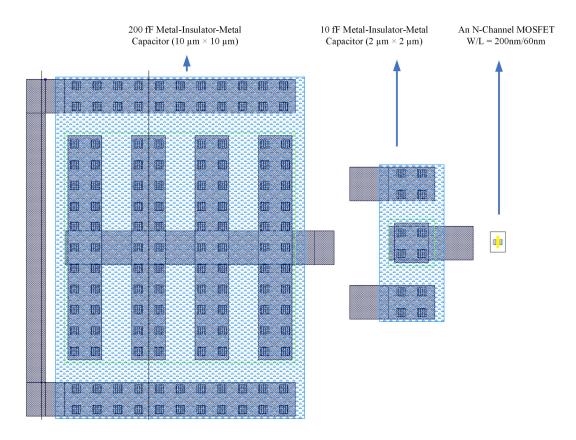

Several aspects make silicon photonics an attractive platform for the implementation of passives. The first aspect is the low cost per area which makes it a suitable platform to host bulky passive components such as capacitors, inductors, and antennas. For example, according to [20] the cost per mm<sup>2</sup> for the photonic chip provided by Advanced Micro Foundry (AMF) is \$225 CAD as opposed \$8,775 CAD for a chip implementation in TSMC 28 nm CMOS Process Technology. This is almost 40 times more expensive in this case. Moreover, with more advanced technology nodes, the area that passives occupy becomes increasingly larger compared to the numbers of transistors that could fit within the same area. This makes the implementation of passives inefficient in advanced technology nodes. To give a sense of the size passives can occupy compared to transistors, Fig.2.4 shows the layout standard N-channel MOSFET with a length of 60 nm and a width of 200 nm next to the layout of two metal-insulator-metal (MIM) capacitors in a CMOS 65 nm technology process. The first is a 10 fF capacitor with length and width of 2  $\mu$ m and the second is a 200 fF capacitor. It is evident that even small capacitors occupy much larger valuable area compared to transistors giving motivation to relocating them when possible. Passives such as antennas and inductors could occupy even larger areas. Further, as silicon photonics has a typical minimum feature size above 100 nm, bulky passives fabrication can be done with less advanced photolithography tools compared to advanced CMOS processes.

Another aspect that makes silicon photonics advantageous to use for the implementation

**Fig. 2.4:** Layout of an N-channel MOSFET next to two MIM capacitors illustrating that passives can much larger area compared to transistors.

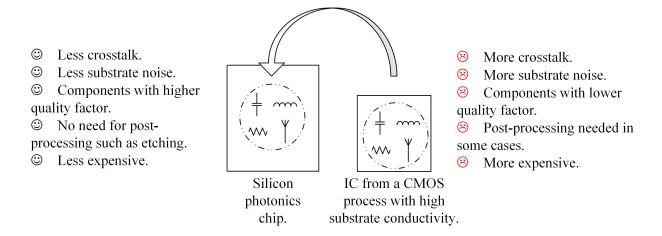

of passives is the low substrate conductivity. In some CMOS processes, the substrate is made conductive to avoid latch-up issues that may damage the chip. While this conductivity is not a problem for digital circuits, it presents a challenge and degrades the performance of analog circuits and RF passives. The silicon photonics process is characterized by its low conductance substrate. This makes it suitable for the implementation of passives with a high quality factor. For example, antennas favor low conductivity substrate. If the substrate is conductive, electromagnetic power is dissipated as heat degrading the radiation efficiency of

the antenna [21]. To avoid this in CMOS processes with high conductivity, etching could be done to thin the substrate to reduce heat losses, but this increases cost. This is avoided when the antenna is implemented in silicon photonics. There are other advantages for low conductivity such as lower crosstalk between components and the suppression of substrate noise.

The benefits of relocating passives from the IC side to the silicon photonics side are summarized in Fig.2.5.

It should be noted the trade-off will be in achieving efficient, cost-effective packaging of the IC chip and the silicon photonics chip. This will depend on the specific application and may lead to other trade-offs such as increased complexity or higher power consumption.

To show the feasibility of designing passives in silicon photonics, experimental demonstrations of implementations of an RC filter driven by a photodetector, a moving average filter, and an antenna are presented in this thesis.

## 2.1.2 A note on process variations in Silicon Photonics

Process variations are an essential consideration when designing passives in the silicon photonics platform. It is, therefore, critical to design for robustness. This can be done by running corner simulations and Monte Carlo simulations and then taking the results into account during the design phase. Additionally, because the process lacks MOSFET switches, it might be needed to include feedback circuits from the IC to the SiPh side to

**Fig. 2.5:** Summary of benefits of relocating passives from the IC side to the silicon photonics side.

stabilize the performance of the passives. An example of this technique is presented in [3], where a thermal tuning loop is used to stabilize the microring drop filter resonance wavelength.

## 2.2 Motivation for optical versus electronic delay lines

Delay lines are used in many applications such as time-to-digital converters (TDCs) and digital-to-time converters (DTCs) for the digitization of short time intervals. They are also used in clock generation and clock distribution applications. Moreover, they are used in signals deskew applications and for edge alignment.

Optical delay lines will be used heavily in the next three chapters. Consequently, in this section, several CMOS and optical delay lines are reviewed and compared in terms of

resolution, delay range, power consumption, and tunability. This comparison will highlight the potential benefits of optical delay lines as compared to electronic delay lines. Subsection 2.2.1 describes some of the most used electronic delay lines. Subsection 2.2.2 describes recent developments of optical delay lines. Subsection 2.2.3 briefly addresses some of the considerations for selecting the optimum delay line for a given application.

#### 2.2.1 CMOS Delay Lines

Electronic delay lines are the most commonly used due to their low complexity and low cost. These delay lines can have a single output or can have multiple outputs where the output corresponding to the required delay is selected. Delay line elements can be tuned with an analog signal or can be digitally controlled. Four different delay line architectures are reviewed in this subsection.

#### Inverter-based tapped delay line and single output delay line architectures

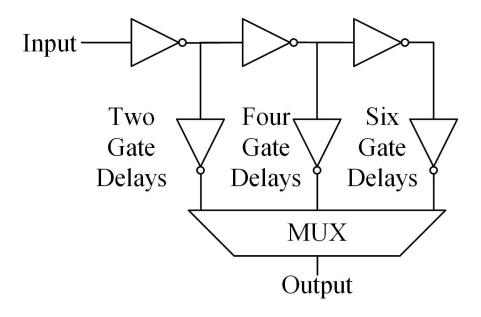

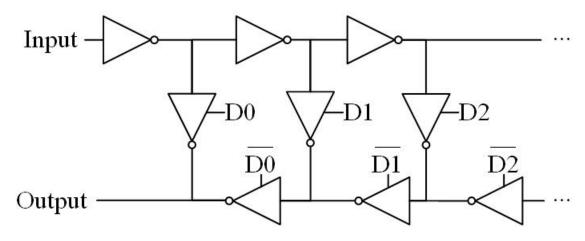

In the inverter-based tapped delay line architecture [22], delay line elements are cascaded and the output corresponding to the required delay is selected. The most commonly used delay element is an inverter, but other delay elements such as flip-flops [23] can be used as well. This architecture is shown in Fig. 2.6. A mux is needed to select the required delay. Alternatively, the single output implementation is shown in Fig. 2.7 and could be used to eliminate the multiplexer. This delay line is digitally controlled using tri-state inverters that

Fig. 2.6: Inverter-based tapped delay line.

are enabled and disable based on the required delay.

These architectures can have a wide delay range and the range increases with the number of stages, but the resolution is limited to twice the gate delay of the delay element. Since the resolution is set by the gate delay, it improves with the technology node where smaller nodes allow for finer resolutions. The power consumption of this type of delay line is high and increases with delay range as more delay elements are needed. These two delay lines can only be exclusively used with digital signals such as clocks.

#### Sub-gate resolution two-path delay line

The architecture in Fig. 2.8 allows for sub-gate delays. In this architecture [24], the digital input signal is fed to two different paths with a different delay (fast path and slow path).

Fig. 2.7: Single output delay line.

MOS capacitors are used to slow down the signal in the lower slow path. The difference between the two paths is less than a gate delay and hence a sub-gate delay is achieved. The control signal is used to enable the appropriate path based on the required delay. The delay range of this technique is limited, and the power consumption is higher than the previous architectures discussed for a given range. This delay line does not scale linearly.

Fig. 2.8: Two path delay line capable of sub-gate delays.

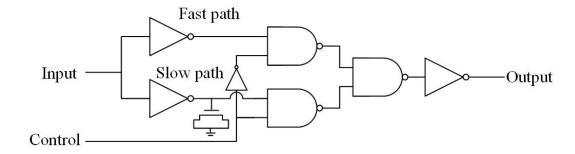

#### Analog delay buffer based delay lines

A delay line element that can be used to build analog delay lines is the analog buffer shown in Fig. 2.9 [25]. This delay line is controlled by an analog signal and the delay is adjusted by varying the control voltages  $V_C$  and  $V_{CB}$  which in turn changes the load of the circuit changing the speed of the buffer. Analog buffer-based delay lines can have good resolution but are power-hungry due to static power consumption.

Fig. 2.9: Analog buffer that can be used to delay analog signals and controlled through adjusting the load.

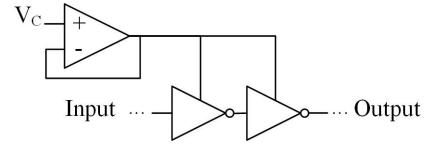

#### Supply voltage controlled and current starved delay lines

In these types of delay lines, either the supply voltage is used to control the delay of the delay line (Fig. 2.10) using an analog signal [26], or the biasing current is changed using a digital signal (Fig. 2.11) [27]. In either case, the current drawn is changed and the rate at which the load capacitor is charged changes accordingly. The first technique requires a supply source capable of providing substantial amounts of current and the resulting delay is not as fine as other techniques. The second technique is reported to achieve good resolution and range [27].

Fig. 2.10: Supply controlled delay line.

## 2.2.2 Optical delay lines

Optical delay lines can be divided into mechanically controlled free space delay lines, passive optical delay lines, and electronically controlled delay lines. Optical delay lines modeled throughout the thesis as shown in Fig. 2.12

Fig. 2.11: Current starved delay line.

Fig. 2.12: Optical delay line model.

#### Mechanically controlled free space delay lines

In this kind of optical delay lines, a gap opening is controlled mechanically changing the distance the light must traverse and thus controlling the delay. Products of these delay lines are readily available (e.g. Santec ODL-330 [28]) and can have delay ranges of 400 ps. The resolution is mechanically controlled and can be as small as 0.2 ps. As those delay lines are passive, they consume no power. Free space delay lines can attenuate the signal and have an insertion loss in the order of 1.5 dB. While those delay lines can have an impressive resolution and range, without consuming power, they are not suitable for integrated systems

due to their large gap size (45 mm in case of ODL-330) and the need for mechanical delay control.

#### Passive integrated optical lines

This delay line is implemented using an optical waveguide of a certain length corresponding to a fixed required delay. This delay line can be implemented on-chip and is suitable for integration with electronic receivers and systems. Those delay lines can have a small size with a compact layout depending on the required delay. For example, in [18] for a 100 ps delay line of 7.2 mm in length, the rectangular nested layout has a size of 250  $\mu$ m × 250  $\mu$ m. This delay line has low insertion loss as well which can be as low as 0.2 dB for 50 ps delay. Since those delay lines are passive, they consume no power. Those delay lines are not tunable but can have accurate delays. An error of 3 ps can be expected for a 50 ps delay [18]. This kind of delay lines will be used extensively in this thesis and is described in more details in subsection 2.4.

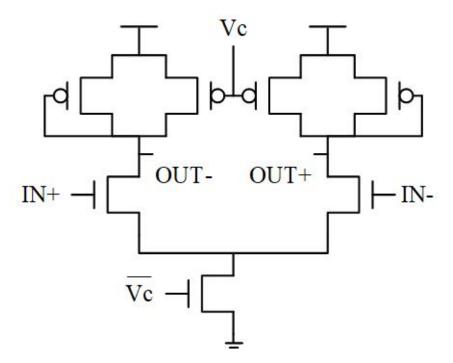

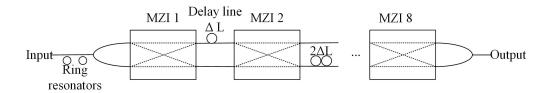

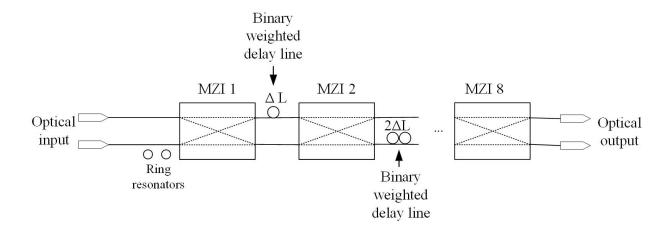

#### Electronically controlled optical delay lines

Integrated optical tunable delay lines can be made tunable by using ring resonators and Mach–Zehnder interferometers (MZIs). One such implementation is reported in [29] and is shown in Fig. 2.13. In this implementation, a ring resonator is used to fine control the delay and can have a continuous delay range of up to 23 ps. The MZI array of eight elements

is used as a coarse delay where they are used to select the delay path. This technique is reported to allow for a continuous delay of up to 1.27 ns. The power consumption can range between 12–33 mW depending on the delay. This delay line has a high insertion loss of 12.4 dB.

Fig. 2.13: Electronically tunable optical delay lines.

#### 2.2.3 Trade-off considerations

When selecting the appropriate delay line, the requirements of the application need to be considered. Considerations include power consumption, resolution, range, tunability, tuning mechanism and signal, integrability, and type of input signal (electrical, optical, analog, digital).

All electronic delay lines reviewed can be used exclusively with digital signals, except for the analog buffer. Moreover, chaining analog buffers to increase the range limits the bandwidth of the chain making this type of delay lines only suitable for slow analog signals or short delays. Optical delay lines have no limitation on the type of information the optical signal carries, digital or analog.

As discusses in the previous subsection, electronic delay lines exhibit a trade-off between